68

Chapter 5: Troubleshooting

modes of unloading data from the acquisition RAM devices. These modes are

setup by writing to registers in the Memory Controller FPGAs. These FPGAs

sequence the data and perform data decoding based on the mode.

DMA Test.

The purpose of this test is to check the various modes of unloading

data from the acquisition RAM memories using DMA backplane transfers. This

test is essentially the same as the Memory Unload Modes Test except that DMA

backplane transfers are used to read the data from the board.

HW Accelerated Search Test.

This test verifies the Memory Controller FPGA-

based HW Accelerated Search function.

Chip Registers Read/Write Test.

The purpose of this test is to verify that each

writable bit in each register of the Analysis chips can be written with a 1 and 0

and read back again. The test also verifies that a chip reset sets all registers to

their reset condition (all 0s for most registers).

LA Chip Calibrations Test.

The purpose of this test is to verify that each

analysis chip in the module is able to successfully complete self-calibration.

Analyzer Chip Memory Bus Test.

The purpose of this test is to check the

Analysis chip memory busses that go between the Analysis chips and the Memory

Controller FPGAs.

System Clocks Test.

The purpose of this test is to verify that the four clocks (1/

2/3/4) are functional between the master board and all Analysis chips, and that

the two Psync lines (A/B) are functional between the master board's Analysis

chips and all Analysis chips in the module. This test verifies that the four clock

lines are driven from the master board and can be received by all Analysis chips,

and that the Psync lines can be driven by each master chip on the master board

and received by all other Analysis chips in the module.

Turbo Clock Divider Test.

The logic analyzer has a clock divider on the board,

used for single edge turbo state. This test verifies that the divider routing works,

and that it resets low.

System Backplane Clock Test.

The purpose of this test is to verify the system

backplane 100 MHz clock is functional to each Analysis chip and running at the

correct frequency. This test also verifies that the PLL in each chip can be

configured in bypass mode (PLL is not used), then verifies that the PLL can be

enabled and used to generate additional clock frequencies.

Comparators Test.

The purpose of this test is to verify that the front-end signal

comparators are able to be set to maximum and minimum thresholds and that

they are able to recognize activity on each input using the cal input clock.

Inter-chip Resource Bus Test.

The purpose of this test is to verify that the

Inter-chip Resource lines (ICRs) can be driven as outputs and received as inputs

Summary of Contents for 16900 Series

Page 3: ...3 Chapter The 16910A Logic Analyzer The 16911A Logic Analyzer...

Page 8: ...8 Contents...

Page 14: ...14 Chapter 1 General Information...

Page 18: ...18 Chapter 2 Preparing for Use...

Page 61: ...61 4 Calibrating This chapter gives you instructions for calibrating the logic analyzer...

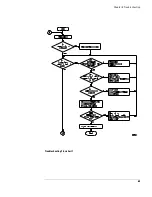

Page 65: ...65 Chapter 5 Troubleshooting Troubleshooting Flowchart 1...

Page 66: ...66 Chapter 5 Troubleshooting Troubleshooting Flowchart 2...

Page 82: ...82 Chapter 5 Troubleshooting To test the cables 18 Return to the troubleshooting flow chart...

Page 94: ...94 Chapter 7 Replaceable Parts 16910A Exploded View Exploded view of the 16910A logic analyzer...

Page 95: ...95 Chapter 7 Replaceable Parts 16911A Exploded View Exploded view of the 16911A logic analyzer...

Page 96: ...96 Chapter 7 Replaceable Parts...

Page 102: ...102 Index...