J2 P15

+8 dBm

+12 dBm

J2 P6

+2 dBm

J2 P19

+7 dBm

J2 P17

+3 dBm

J2 P8

NOTE:

INSTRUMENT SETTINGS TO OBTAIN

LISTED POWER LEVELS ARE AS FOLLOWS:

INSTRUMENT PRESET

CONNECT - 25 dBm 50 MHz SIGNAL TO RF INPUT.

PROVIDES SAME LEVELS AS 50 MHz CAL SIGNAL.

FREQUENCY: 50 MHz

Adc RANGE: AUTO

ECL LEVELS ARE - 0.7 V to - 1.7 V

NOTE:

NOTE 2:

MEASUREMENT VALUE WILL BE ATTENUATED

20 dB (IN A 50 MEASUREMENT SYSTEM) UNDER

THE FOLLOWING CONDITIONS.

- WHEN USING THE SMB JACKS ON THE EXTENDER

BORDS (EXCEPT FOR SR_H, SR_L, CALOSC_L,

CALOSC_H, AND 10 MHz AIF. THESE SIGNALS MUST

BE MEASURED AT THE ZERO OHM RESISTORS.)

- WHEN USING A10,TP5.

Ω

NOTE 1:

VALUES

MEASURED WITH HIGH FREQUENCY

PROBE. SUBTRACT 6 dB IF PROBE NOT USED.

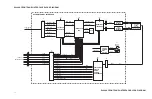

E4406A OVERALL BLOCK DIAGRAM

E4406A OVERALL BLOCK DIAGRAM

RF

INPUT

7 MHz - 4 GHz

P2

RF IN

W9

J1 P13

AT1

- 7dB

50 MHz_CAL_IN

(From A18)

+2.5 dBm

(Note 2)

+ 13 - + 15 dBm

W11

P4

- 32 dBm

A17 RF ASSEMBLY

A18 REFERENCE ASSEMBLY

A19 SYNTHESIZER ASSEMBLY

BANDPASS FILTERS

1ST DOUBLER

2ND DOUBLER

321.4 MHz

0 - 40 dB

1 dB STEPS

10 dB

IF CALIBRATOR

321.4 MHz

- 36 dBm

+ 7 dBm

+ 7 dBm

300MHz

+ 23 dBm

2nd LO

10 MHz_AIF

FROM A18

REFERENCE

ASSEMBLY

J18

REAR PANEL

EXT. TRIGGER IN

J5

FRONT PANEL

EXT. TRIGGER

P4

W20

J2 P2

+5 dBm

W5

P1

21.4 MHz

- 19 dBm

(Note 1)

P1

21.4_OUT

CAL SWITCH

IMAGE FILTER

6 dB

6 dB

CAL_OSC_HI

(From A12)

CAL_OSC_LO

(From A12)

LO_IN

250 MHz - 4 GHz

> + 10 dBm

(From A19)

.5 MHz - 2.5 MHz

DIV 2-13

J2 P13

L_OXCO_TUNE

LINTREF

ON/OFF

10 MHz FREQUENCY

REFERENCE

EXT_REF_IN

1 MHz - 30 MHz

FROM A15

DAUGHTERBOARD

DAC

PHASE

DETECTOR

10 MHz_SYNTH

FROM A18

REFERENCE

ASSEMBLY

ABUS to A15

DAUGHTERBOARD

+ 10V

P3

PIN15

sa81a

VCO

500 - 1000 MHz

250 - 500 MHz

628 - 1000 MHz

396 - 628 MHz

500 - 1000 MHz

VARIABLE

ATTENUATOR

100 MHz

VCXO

J1 P18

J2-P2

300 MHz

+ 11.5 dBm

(Note 2)

REF_50 MHz

+2.5 dBm

TO 50 MHz_CAL_IN

ON A17 RF ASSEMBLY (Note 2)

10 MHz_REF_OUT

L EXT_OUT_OFF

L50 MHz_CAL_ON

10 MHz_CPU

10 MHz_RF

10 MHz_AIF

10 MHz_OPT

10 MHz_SYNTH

Φ ƒ

Φ ƒ

LOOP

FILTER

& LEAD/

LAG

FRAC-N

DIVIDE

FRAC-N

DIVIDE

250 - 396 MHz

1.0 - 1.26 GHz

2.0 - 2.52 GHz

1.26 - 1.6 GHz

2.5 - 3.2 GHz

1.6 - 2.0 GHz

3.2 - 4.0 GHz

2

x

2

x

2

MUX

ABUS_RF_OUT

PRE_LEVEL_DRIVE

TO A17 RF ASSEMBLY

2 to 3 Vdc

LO OUT

250 MHz - 4GHz

> + 10dBm

W11

W13

P9

P7

IF_IN_SEL

IF_SEL

BB_SEL

P4 PIN62

7.5 MHz

-15 dBm

(Note 1)

P8

P4 PIN 27

P4 PIN 55

P4 PIN 54

P4 PIN 29

P4 PIN 23

P4 PIN 25

W2

W1

TO DAUGHTERBOARD

P2

PIN 9

A15 P1

J6

P3 P17

ABUS_LOOP

ABUS_10V

IF

RF

LO

IF

RF

LO

IF

RF

LO

R

FRAC-N

DIVIDE

10 or 12.5 MHz

6

MODULUS CONTROL

4

2

5

x

3

A12 ANALOG IF ASSEMBLY

A10 DIGITAL IF ASSEMBLY

A27 REAR PANEL I/O

A15 DAUGHTERBOARD

PREFILTERS LC

W12

J13

AUTORANGE ( 21.4 MHz )

J9 P62

12.5 MHz LPF

7.5 MHz

7.5 MHz BPF

(2 MHz BW)

21.4 MHz

(10 MHz BW)

28.9 MHz

3rd LO

42.8 MHz

30 MHz

30 MHz

VIDEO

DATA_OUT

CAL. OSC.

SAMPLE RATE OSC.

XTAL

OUT OF LOCK

DETECTOR

IF

RF

LO

BW =

7.5 MHz

to 200 kHz

BW =

200 kHz

to 2.5 kHz

CALOSC_TRIG

J9 P29

J9 P23

J9 P25

J9 P55

J9 P54

J9 P52

+

-

GATE_TRIG

SWEEP_ARM

SWEEP_TRIG

FGET

OPT TRIG 1

OPT TRIG 2

LINE_TRIG

INTERP_CAL _TRIG

EXT TRIG 1

EXT TRIG 2

BURST

CARRIER

TRIGGER

SAMPLE RATE HI

SAMPLE RATE LO

PS_FREQ TO

A6 POWER SUPPLY

244 10 KHz

FM RATE=10 Hz

PLL

PLL

PLL

CAL_OSC_LO TO A17

CAL_OSC_HI TO A17

J9 P27

GATE_ARM

J9 P59

J9 P60

“Q” FROM FRONT PANEL

P2

7.5 MHz IF_OUT

“I” FROM FRONT PANEL

TRIGGER

ECL

PEAK

DETECTION

GAIN

RANGE

SELECT/RULES

12

TP5 -20.5 dBm

(Note 2)

TP1

ABUS

16

32

3

GAIN

LOOK _UP

TABLE

ASIC/ZOOM

FILTER

DIGITAL IF

PROCESSING CHIP

CPU

ASSY

Keyboard

SCSI

Digital

I/O

A22

A25

PCI BUS

BB_SEL

ADDR_BUS

OFFSET

ADJUST

DITHER

GENERATOR

SCLK

P4 PIN 78

P4 PIN 76

P4 PIN 77

P4 PIN 74

P4 PIN 73

P4 PIN 75

P4 PIN 79

P4 PIN 72

MOSI_BUS

LDATA

TO

MOTHERBOARD

MISO

LSRQ

LCNTRL

LADDR

HPUP

30 MHz

J2

J3

J1

J2

W25

J31 P13

EXT_REF_IN

(To A18)

10 MHz_REF_OUT

(From A18)

J31 P2

J1 P36

TRIG1

TRIG2

J1 P37

J4

J5

ADC

TP 5

Power

- 14 dBm

- 20.5 dBm

- 26.5 dBm

- 33 dBm

- 39 dBm

- 45 dBm

ADC

Range

+24 dB

+18 dB

+12 dB

+ 6 dB

0 dB

- 6 dB

SERIAL

BUS

TO A15 DAUGHTERBOARD

10 MHz OUT (SWITCHED)

TO DAUGHTERBOARD

A15 J31

(Note 2)

2

321.4 MHz

- 25 dBm

(Note 1)

INTERPOLATER

CAL

TRIGGER

CAL OSCILLATOR

SEQUENCE

GENERATOR

P3

321.4_OUT

VIDEO PEAK

DETECTOR

VREF

ECL

POWER

SUPPLY

SWITCHING

REFERENCE

TIMING

DATA_BUS

ADDR_BUS

DATA_BUS

16

16

16

EXT REF IN

(1-30 MHz)

10 MHz OUT

(SWITCHED)

TRIGGER 1 OUT

TRIGGER 2 OUT

REFERENCE

UNLOCK

DETECTOR

J9 P57

P4 PIN 70 TRIGGER_OUT/TRIG2

P4 PIN 71 HSWP_OUT/TRIG1

3

6

5

8

2

1

16

J1 P13

PRE_LEVEL_DRIVE

(to A19)

2 to 3 Vdc

J1 P18

ECL

J18 21.4 MHz

NORMAL 2V p-p

(4V p-p MAX)

J12

Range

Clock

J11

J4

Sample Rate

(ECL Levels)

Summary of Contents for E4406A VSA Series

Page 4: ...4 ...

Page 10: ...10 Contents ...

Page 11: ...11 1 Troubleshooting ...

Page 66: ...66 Chapter1 Troubleshooting How to Return Your Instrument for Service ...

Page 67: ...67 2 Block Diagrams ...

Page 119: ...Chapter 2 119 Block Diagrams Block Diagrams Block Diagrams ...

Page 120: ...120 Chapter2 Block Diagrams Block Diagrams ...

Page 122: ...122 Chapter2 Block Diagrams Block Diagrams ...

Page 124: ...124 Chapter2 Block Diagrams Block Diagrams ...

Page 125: ...125 3 Parts List ...

Page 164: ...164 Chapter3 Parts List Hardware ...

Page 165: ...165 4 Assembly Replacement ...

Page 169: ......

Page 170: ...170 Chapter4 Assembly Replacement Removal and Replacement Procedures ...

Page 227: ...Chapter 4 227 Assembly Replacement Front Frame Subassemblies Figure 4 39 Keypad Parts ...

Page 231: ...231 5 Post Repair Procedures ...

Page 262: ...262 Chapter5 Post Repair Procedures Automated Adjustments ...