A49 IF MULTIPLEXER

FROM

A16

P1

FROM A16J15

W36

J1

+5V

From

Rear Panel

(Option H11)

From

Rear Panel

(Option H11)

From

Rear Panel

(Option H11)

From

Rear Panel

(Option H11)

B PULSE IN

J404

J403

J402

J401

50

50

3 MHz

B0

B1-15

R2 PULSE IN

J304

J303

J302

J301

50

50

3 MHz

B0

B1-15

R1 PULSE IN

J204

J203

J202

J201

50

50

3 MHz

B0

B1-15

J103

J102

A PULSE IN

J104

J101

50

50

3 MHz

B0

B1-15

A3 FRONT PANEL INTERFACE

USB

HUB

DISPLAY

CONTROL

ICRO CONTROLLER

SPEAKER

INVERTER

A2

DISPLAY

TOUCHSCREEN

& CONTROLLER

A1

KEYPAD

RPG

USB

BOARD

M

EXT REF IN

10 MHz

8.333 MHz

1.0416 MHz

B1 - 15

2nd LO x4

33.1667 MHz

J4

W33

W32

216

5

5

96

12

10 MHz

HIGH STAB

OCXO

100 MHz

PHASE LOCK REF

A10 FREQUENCY REFERENCE

215

211

218

212

B0

B1-15

213

10 MHz

J2

J5

LOCAL

DIGITAL

BUS

POWER

BUS

DC BIAS 1

A16 TEST SET

MOTHERBOARD

DC BIAS 2

W31

2

J5

PORT 1

BIAS

INPUT

PORT 2

BIAS

INPUT

200 Hz

3

R

I

L

99.50 MHz

214

500 kHz

20

217

200 Hz

R

I

L

ALC

ALC

2

1.5 GHz

B2-15

J106

J101

B0-1

2.4 GHz

3 GHz

750 MHz

A8 FRACTIONAL-N SYNTHESIZER

414

417

415

413

412

1.5 - 3.0 GHz

VCO

2250 MHz

VCO

418

Level

Adjust

B3-15

B2

416

LOCAL

DIGITAL BUS

POWER

BUS

5 MHz REF

J105

FRAC-N

LOGIC

FRAC-N

LOGIC

1

1

B0-1

B2-15

BIAS/RF

LOMA10

X2

B8 -10, 12 -15

7.6 - 10.0

GHz

4.8 - 6.0

GHz

3.0 - 3.8 GHz

3.8 - 4.8

GHz

B0-3

B4-15

6.0 - 7.6

GHz

B4 - 7, 11

2

2

X2

X2

10.0-12.8 GHz

15.0 GHz

B0 - 10

B11 - 15

0.01-20

GHz

11 GHz

X2

12.8 - 16.0

GHz

16.0 - 20.0

GHz

3

3

W19

W20

W18

W11

W12

W13

W14

A20 L.O. DISTRIBUTION

ASSY (LODA)

W17

W16

W15

A19 SPLITTER

W17

W17

FROM

A16

11 GHz

10.0-12.8 GHz

12.8 - 16.0

GHz

15 GHz

16.0 - 20.0

GHz

0.01-20 GHz

B11-15

B0-10

11 GHz

YTO TUNE

FM

A12 SOURCE 20

A22 SWITCH

SPLITTER

A26

TEST PORT

COUPLER

PORT 2

A25

TEST PORT

COUPLER

PORT 1

W10

50

50

4

4

A38

BIAS TEE

A36 STEP

ATTEN

W51

OPTION UNL

W55

DC BIAS 1

0-60 dB

A39

BIAS TEE

A37 STEP

ATTEN

W52

OPTION UNL

W56

DC BIAS 2

0-60 dB

W9

W5

W54

W6

W53

L

I

R

8.0 GHz

5.25 GHz

B4-15

B0-3

SOURCE 10

PMYO

3.8 GHz

3 GHz

3.8 GHz

117

118

11 GHz

B4-15

B0-3

W4

W7

W3

W8

30 db ATTENUATOR

30 db ATTENUATOR

ALC

112

114

SLOPE

COMPENSATION

POWER DAC

TEMP COMP

113

115

116

111

X2

LOCAL

DIGITAL BUS

POWER

BUS

DAC

YTO

3-10 GHz

23 GHz

FROM

A16

W1

FROM

A16

FROM

A16

8.333 MHz

16.667 MHz

FROM

A16

FROM

A16

TO

A35, A17, A18, A20,

A22, A36, A37

HIGH DENSITY DATA BUS

POWER BUS

LOCAL DIGITAL BUS

SERIAL TEST BUS NODES

Bx = ACTIVE SOURCE BAND

MIXED POWER AND CONTROL SIGNALS

FROM

A16

FROM

A16

FROM

A16

FROM

A16

FROM

A16

1V/GHz

(FROM A11)

1V/GHz

(TO A12, A16)

DAC

516

517

518

-15V REF

+9V REF

+15V REF

511

TEST SET IO

INTERFACE

AUX IO

INTERFACE

HANDLER O

INTERFACE

I

TEST SET O

I

AUX O

I

TRIGGER OUT

TRIGGER OUT

TRIGGER IN

HANDLER O

I

LOCAL

DIGITAL BUS

POWER

BUS

411

+5V REF

DAC

40 MHz

313

318

NC

GND

A11 PHASE LOCK

20 MHz

REF IN

J6

COUNTER

AQUIRE: ON

PRETUNE: 30 kHz

SWEEP: 100 Hz

316

DELAY COMP

RAMP CAL

2.5 GHz OFFSET

ANALOG RAMP

DIGITAL PRETUNE RAMP

317

315

312

314

700 kHz

20 MHz 15 MHz

6 MHz

311

NC

B1 - 15

B0

23 GHz

B0

4 MHz

A27 A FIRST

CONVERTER

(MIXER)

LO

MIXER BIAS

W25

W26

W27

W28

A33 RECEIVER R2

A34 RECEIVER B

41.667

kHz

41.667

kHz

41.667

kHz

41.667

kHz

A31 RECEIVER A

A32 RECEIVER R1

I

I

L

L

R

R

0°

90°

2nd LO

2nd LO

a

b

R2

R1

A

B

PHASE

LOCK

MUX

4

To 2nd LO

x 4

a

To 2nd LO

x 4

b

A28 R1

CONVERTER

(MIXER)

FIRST

LO

A29 R2

CONVERTER

(MIXER)

FIRST

A30 B

CONVERTER

(MIXER)

FIRST

LO

J2

J50

B0 = 1.0416 MHz

B1 - 15 = 8.333 MHz

W21

W22

W23

W24

W30

W29

I

I

L

L

R

R

2nd LO

2nd LO

a

b

I

I

L

L

R

R

2nd LO

2nd LO

a

b

I

I

L

L

R

R

2nd LO a

+ 15 dB

0°

90°

0°

90°

0°

90°

2nd LO b

FROM

A16

W40

W14

A35 RECEIVER MOTHERBOARD

40 MHz

FROM

A16

RF

RF

To

Phase Lock

B

B1-15

B0

8.333 MHz

1.0416 MHz

To

Phase Lock R2

B1-15

B0

8.333 MHz

1.0416 MHz

To

Phase Lock R1

B1-15

B0

8.333 MHz

1.0416 MHz

To

Phase Lock

A

B1-15

B0

8.333 MHz

1.0416 MHz

W41

W42

W43

W44

IF

B0 = 1.0416 MHz

B1 - 15 = 8.333 MHz

IF

B0 = 1.0416 MHz

B1 - 15 = 8.333 MHz

IF

B0 = 1.0416 MHz

B1 - 15 = 8.333 MHz

IF

TO A13

(OPTION 080)

I

L

R

I

L

R

LO

R1

R2

B

A

ADC

ADC

ADC

ADC

PCI

BRIDGE

300 kHz

300 kHz

IF Calibration

Signal

300 kHz

300 kHz

A6 SIGNAL PROCESSING

ADC MODULE (SPAM)

J3

A

R1

J5

J6

R2

B

J4

RAM

DSP

USB

RS-232

PARALLEL

GPIB

VGA

USB x 2

LAN

LOCAL DIGITAL BUS

POWER BUS

MAIN

CPU

EEPROM

ROM

RAM

VIDEO RAM

A41 HARD

DISK DRIVE

PCI BUS

PCI BUS

VIDEO PROCESSOR

A15 CPU

A14 SYSTEM MOTHERBOARD

TO A8, A9, A11, A12, A16

USB

INTERFACE

RS-232 PORT

INTERFACE

PARALLEL PORT

INTERFACE

GPIB PORT

INTERFACE

VGA

INTERFACE

10/100 BASE-T

ETHERNET

I

L

R

I

L

R

RF

I

L

R

I

L

R

RF

RF

+ 15 dB

+ 15 dB

40 MHz

+ 15 dB

40 MHz

A43 STEP

ATTEN

W47

W45

OPTION 016

0-35 dB

FROM

A16

A44 STEP

ATTEN

W48

W46

OPTION 016

0-35 dB

FROM

A16

TO

A27

TO

A30

FROM

A25

FROM

A26

40 MHz

+ 15 dB

RF

FROM A13

(OPTION 080)

512

514

713

515

513

A16 TEST SET MOTHERBOARD

TO

A18

MA 20 LO ALC

SLOPE COMP

1V/GHz

(FROM A11)

POWER DAC

814

818

+10V REF

DET VOLTAGE OUT

812

813

+1.78V BIAS REF

PHASE LOCK IF DET

811

816

-10V REF

+5V REF

715

815

+10V REF

-1.25V BIAS REF

EXT REF OUT

10 MHz

W34

J3

20 MHz

REF

10 MHz

5 MHz

REF

J10

TO A9

(OPTION

080)

J12

J11

N/C

2

5 MHz

20 MHz

B0-1

J502

1 GHz

A17 L.O.

10 (LOMA 10)

MULTIPLIER/AMPLIFIER

A18 MULTIPLIER/AMPLIFIER

MULTIPLIER/AMPLIFIER 20 (MA 20)

MULTIPLIER/AMPLIFIER 20 (MA 20)

ƒ

ƒ

ƒ

B0 1.000 MHz 0°

B0 1.000 MHz 0°

9

B1 - 15 8.29167 MHz 0°

B1 - 15 8.29167 MHz 0°

9

PHASE

LOCK

MUX

A4

POWER

SUPPLY

LINE IN

USB

INTERFACE

USB x 4

REAR PANEL

INTERCONNECTS

FRONT PANEL

INTERCONNECTS

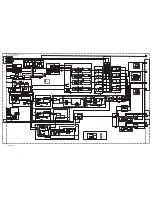

E8362C Overall Block Diagram

(Includes Option UNL and 016)

Service Guide: E8364-90038

m220cblk

2 January 2008

s1

Summary of Contents for E8362C

Page 11: ...Service Guide E8364 90038 1 1 1 Safety and Regulatory Information ...

Page 21: ...Service Guide E8364 90038 2 1 2 General Product Information ...

Page 33: ...Service Guide E8364 90038 3 1 3 Tests and Adjustments ...

Page 81: ...Service Guide E8364 90038 4 1 4 Troubleshooting ...

Page 137: ...Service Guide E8364 90038 5 1 5 Theory of Operation ...

Page 171: ...Service Guide E8364 90038 6 1 6 Replaceable Parts ...

Page 257: ...Service Guide E8364 90038 7 1 7 Repair and Replacement Procedures ...

Page 341: ...Service Guide E8364 90038 8 1 8 General Purpose Maintenance Procedures ...