Performance Tests

3

Installation and Verification Manual

73

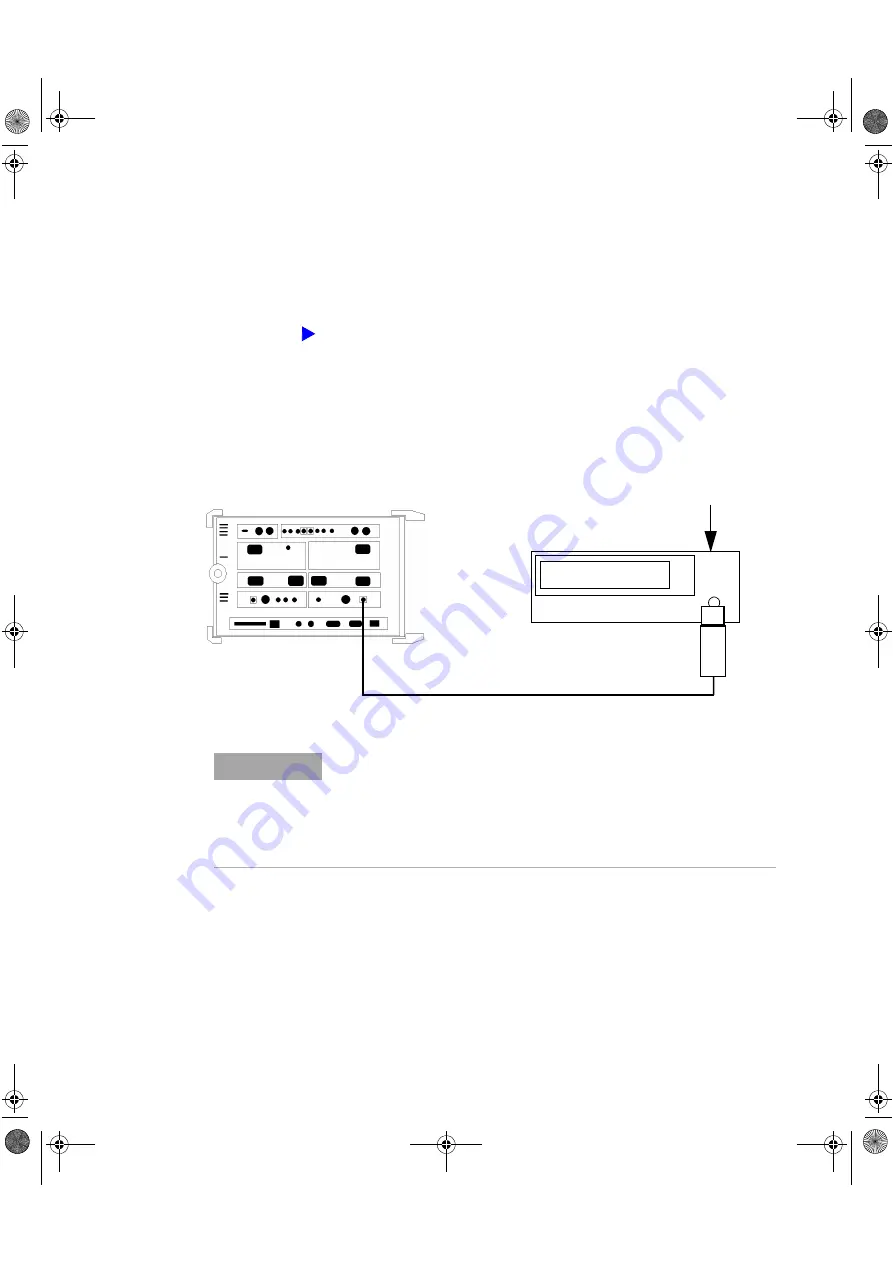

Alternative DS1 Clock test (if suitable DSn Test Set is not available)

1

Connect the OmniBER OTN’s DS1 Clock Out port to the

Frequency Counter Input using a 110/75

Ω

Bal/Unbal

Converter and 75

Ω

termination. Set the Frequency Counter

input impedance set to 1M

Ω

.

2

Adjust the Frequency Counter Trigger Level to obtain a

stable reading and it will also be necessary to increase the

Gating time due to the effects of Framing Bits. Check that the

Frequency Counter reads between:

1.540993 MHz and 1.541007 MHz

3

Alternative Test Complete.

To perform alternative DS1 clock test

N O T E

As the DS1 Clock Output is a Framed All ‘1’s signal the average frequency

measured by the Counter will be less than expected, e.g. 1541000 Hz

rather than 1544000 Hz due to the effects of Framing Bits in the signal. The

Ternary format of the signal can also mean that depending on input

attenuation/trigger setting the counter may trigger on exactly half the

signal rate e.g. 770500 Hz.

DS1

Clock

OUT

Bantam to Bantam Cable

53181A Counter

Bal/UnBal

Converter &

75

Ω

term.

External High Stability

10 MHz Reference may

be required

OmniBER OTN

panther3_iv.book Page 73 Wednesday, January 15, 2003 12:03 PM