CHIPSET FEATURES SETUP

·

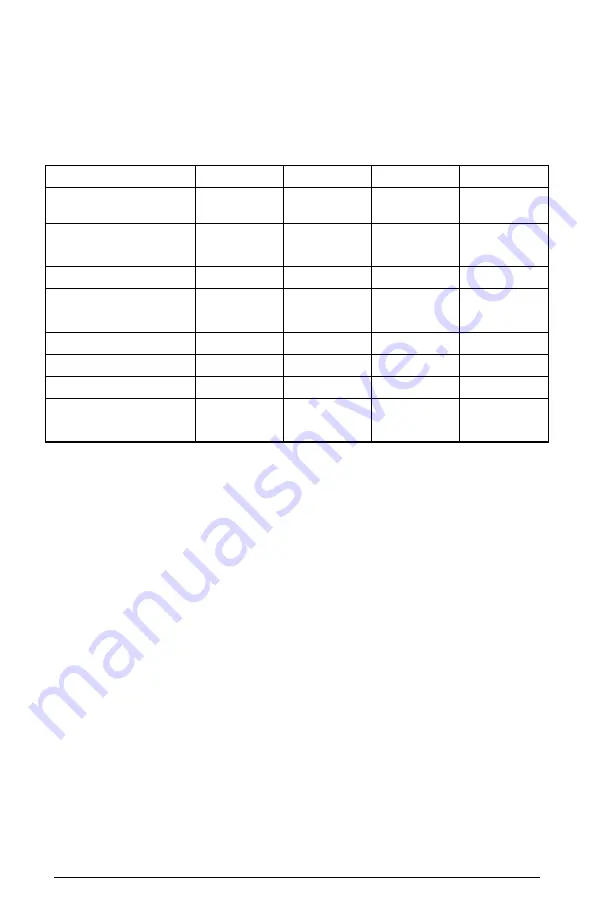

Auto Configuration

: Normally select “Disabled” to manually

control system timing parameters as recommended below.

25 MHz

33 MHz

40 MHz

50 MHz

AT Bus Clock

CLK/3 or

CLK/6

CLK/2 or

CLK/4

CLK/2.5 or

CLK/5

CLK/3 or

CLK/6

SRAM Read

Burst

3111

3222

3222

3222

SRAM Write WS

0WS

0WS

1WS

1WS

Special SRAM

Wait State (WS)

Disabled

Enabled

Disabled

Disabled

DRAM Write WS

0WS

1WS

1WS

1WS

DRAM Read WS

2WS

3WS

3WS

3WS

RAS Precharge

2 Sysclk

3 Sysclk

3 Sysclk

3 Sysclk

RAS to CAS

Delay

1 Sysclk

1 Sysclk

2 Sysclk

2 Sysclk

·

F0000 Cacheable

: When enabled, the system BIOS block F (F0000h-

FFFFFh) address range will be cacheable.

·

C0000 Cacheable

: When enabled, the Video BIOS block C (C0000h-

C7FFFh) address range will be cacheable.

·

Cacheable Range

: The range of addresses that are cacheable.

Default all DRAM addresses are cacheable up to 128MB.

·

DRAM Page Mode

: Normally select Slow Page Mode.

·

15-16MB Access

: In Normal mode, access to address 15-16MB range

will be mapped to local DRAM memory. Some Video Capture cards

require that this area must be mapped to AT memory space.

·

1MB Cache Memory

: Enabled if 1MB of cache is installed. Else

disabled.

·

VGA Type

: If "Standard" is selected, BIOS will support any kinds of

VGA cards (PCI, ISA, and VESA). However, minor performance will

be degraded due to extra decoding. In "PCI" mode, BIOS will only

Page 32 486VP System Board User's Manual

Summary of Contents for 486VP

Page 1: ...486VP VL PCI System Board USER S MANUAL Revision 1 0...

Page 9: ...3 6V 60mA on board battery Page 8 486VP System Board User s Manual...

Page 11: ...Page 10 486VP System Board User s Manual...

Page 12: ...FIGURE 486VP System Board User s Manual Page 11...

Page 29: ...PG UP PG DN Modify the Setup Item Page 28 486VP System Board User s Manual...