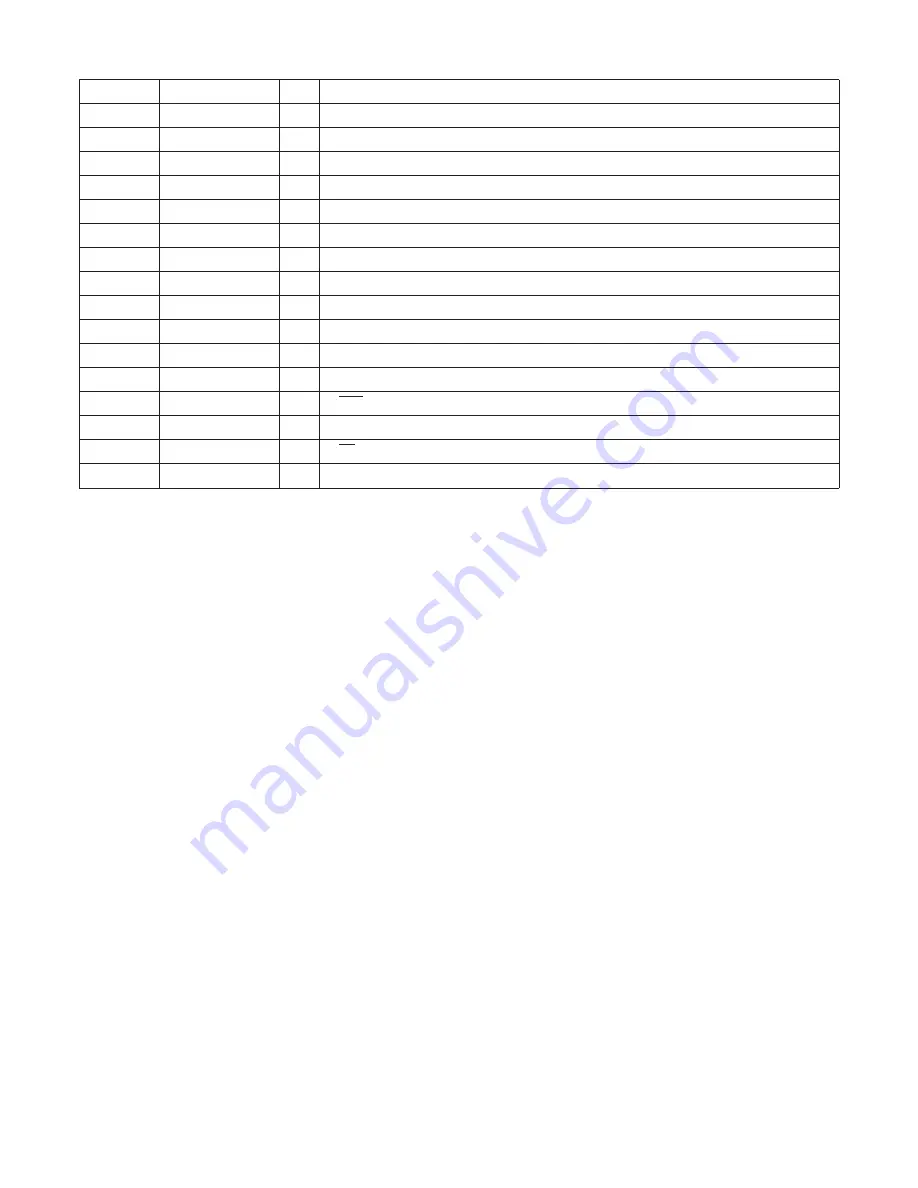

– 2

1

–

85

MD0

I/O

Data input and output signal output terminal to DRAM (Not connected).

86

DI

I

Data input terminal for CPU interface.

87

VDD1

–

Internal power supply terminal.

88

DO

O

Data output terminal for CPU interface.

89

VDD2

–

Power supply terminal.

90

VSS

–

Ground terminal.

91

MD3

I/O

Data input and output signal output terminal to DRAM (Not connected).

92

WRQB

O

Interrupt signal output terminal for CPU interface.

93

INTB

O

Interrupt signal output terminal for CPU interface.

94

ADIPWO

I

Wobble signal input terminal.

95

MD2

I/O

Data input and output signal output terminal to DRAM (Not connected).

96

SHOCK

O

SHOCK / RFNG output terminal.

97

MCASB

O

CAS signal output terminal to DRAM (Not connected).

98

PCK

O

VCEC system clock signal output terminal.

99

MOEB

O

OE signal output terminal to DRAM (Not connected).

100

VCVSS

–

Ground terminal for VCEC.

Pin No.

Pin Name

I/O

Description

Summary of Contents for AM-CL33

Page 14: ... 14 SCHEMATIC DIAGRAM 1 MAIN ...

Page 16: ... 16 IC BLOCK DIAGRAM ...