-43-

MUTE

DEEM

CKO

DVSS

BCKI

DI

DVDD

LRCI

TSTN

TO1

AVDDL

LO

AVSS

RO

AVDDR

MUTEO

XVDD

XTI

XTO

XVSS

DS

RSTN

MODE

ATCK

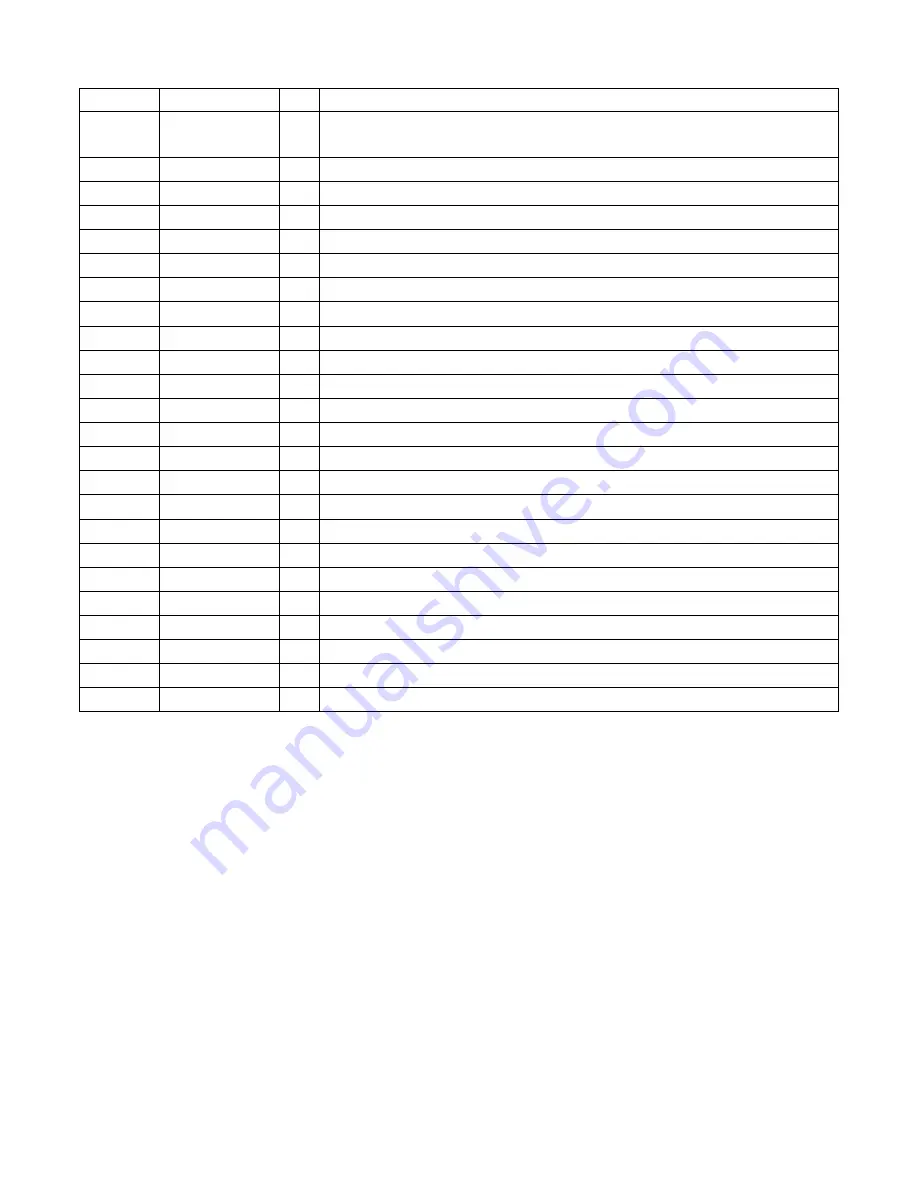

IC, SM5878M

Pin No.

Pin Name

I/O

Description

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

I

I

O

—

I

I

—

I

I

O

—

O

—

O

—

O

—

I

O

—

I

I

I

I

MODE = H: Soft mute ON/OFF terminal. (Mute at H).

MODE = L: Attenuator level DOWN/UP terminal. (DOWN at H). (Pull down)

De-emphasis ON/OFF terminal. (De-emphasis ON at H).

Oscillator clock output. (16.9344 MHz).

Digital VSS terminal.

Bit clock input terminal.

Serial data input terminal.

Digital VDD terminal.

Sample rate clock (fs) input terminal. (H = L ch/L = R ch).

Test input. (“H” or open during normal operation). (Not connected)

Test output 1. (Normally low level output). (Not connected)

Analog VDD terminal. (For L ch).

Left channel analog output terminal.

Analog VSS terminal.

Right channel analog output terminal.

Analog VDD terminal. (For R ch).

Infinity zero detection output.

X’tal system VDD terminal.

X’tal oscillator terminal. (Or external clock input terminal of 16.9344 MHz).

X’tal oscillator terminal.

X’tal system VSS terminal.

Double-speed/normal playback selection. (Double-speed at H). (Connected to ground)

Reset terminal. (Reset at L).

Soft mute/Attenuator mode selection. (Soft mute at H). (Not connected)

Attenuator level setup clock (Ignored when MODE = H). (Not connected)

Summary of Contents for LCX-K117

Page 12: ... 12 SCHEMATIC DIAGRAM 1 MAIN 2B 1 2 DECK 2B Q243 244 ...

Page 13: ... 13 SCHEMATIC DIAGRAM 2 MAIN 2B 2 2 2B ...

Page 16: ... 16 SCHEMATIC DIAGRAM 3 VCD 1 2 2B ...

Page 17: ... 17 SCHEMATIC DIAGRAM 4 VCD 2 2 DAC_CK V ID ...

Page 18: ... 18 SCHEMATIC DIAGRAM 5 FR LED 2B D ...

Page 20: ... 20 SCHEMATIC DIAGRAM 6 PT PTX901 ...

Page 24: ... 24 FL AIWA4239ACL 13 GRID ASSIGNMENT ANODE CONNECTION GRID ASSIGNMENT ANODE CONNECTION ...

Page 25: ... 25 VOLTAGE CHART ...

Page 26: ... 26 ...

Page 27: ... 27 ...

Page 28: ... 28 ...