– 29 –

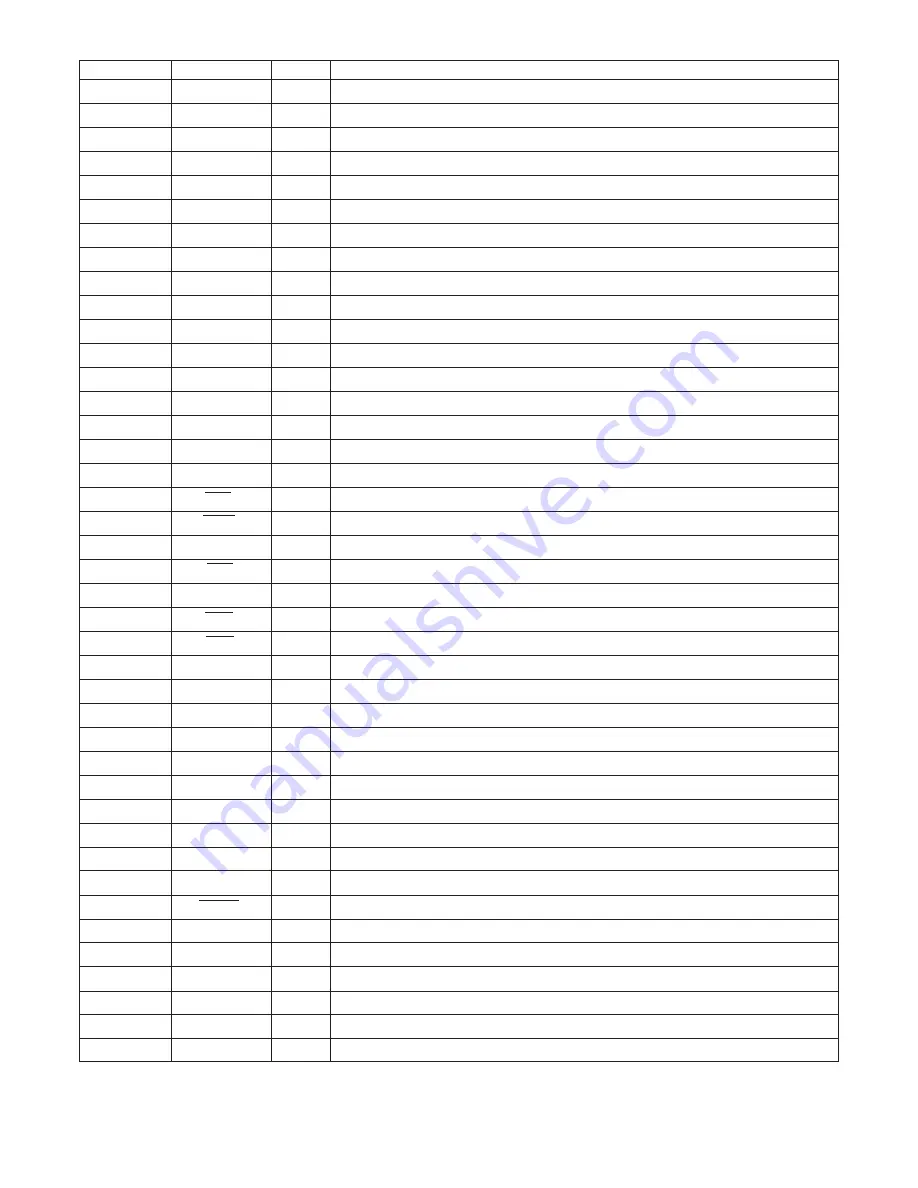

Pin No.

Pin Name

I/O

Description

IC, CL680-D1

1

NC

–

Not connected.

2

VSS

–

GND.

3

CD BCK

I

Bit clock input from CD DSP.

4

CD DATA

I

Data input from CD DSP.

5

CD LRCK

I

LRCK input from CD DSP.

6

CD C2PO

I

C2 pointer input from CD DSP.

7 ~ 9

NC

–

Not connected.

10 ~ 15

MD0 ~ MD5

I/O

DRAM/ROM interface. (DATA)

16

VSS

–

Ground.

17

MD6

I/O

DRAM/ROM interface. (DATA)

18

VDD3

–

Power supply 3.3V.

19

MD7

I/O

DRAM/ROM interface. (DATA)

20

VSS

–

Ground.

21

MD8

I/O

DRAM/ROM interface. (DATA)

22

VDD3

–

Power supply 3.3V.

23 ~ 29

MD9 ~ MD15

I/O

DRAM/ROM interface. (DATA)

30 ~ 36

NC

–

Not connected.

37

MCE

–

ROM chip enable.

38

MWE

O

DRAM write enable.

39

VSS

–

Ground.

40

CAS

O

DRAM/ROM interface.

41

VDD3

–

Power supply 3.3V.

42

RAS0

O

DRAM/ROM interface.

43

RAS1

O

DRAM/ROM interface. (Not used)

44 ~ 46

MA10 ~ MA8

O

DRAM/ROM interface. (Address)

47

VSS

–

Ground.

48

MA7

O

DRAM/ROM interface. (Address)

49

VDD3

–

Power supply 3.3V.

50 ~ 52

MA6 ~ MA4

O

DRAM/ROM interface. (Address)

53

VSS

–

Ground.

54

MA3

O

DRAM/ROM interface. (Address)

55

VDD3

–

Power supply 3.3V.

56 ~ 58

MA2 ~ MA0

O

DRAM/ROM interface. (Address)

59

PGIO7

I/O

Programmable I/O. (Not used)

60

RESET

I

Reset input.

61

VDD MAX IN

I

Power supply - VDDMAX. (5.0V)

62 ~ 64

NC

–

Not connected.

65

AGND DAC

–

Analog ground.

66

AVDD DAC

–

Analog power supply (DAC) : 3.3V.

67

COMPOS OUT

O

Composite out.

68

AGND DAC

–

Analog ground.

Summary of Contents for NSX-VC8

Page 12: ...SCHEMATIC DIAGRAM _ 1 MAIN 1 2 AMP SECTION 12 ...

Page 13: ...SCHEMATIC DIAGRAM _ 2 MAIN 2 2 TUNER SECTION 13 ...

Page 14: ...SCHEMATIC DIAGRAM _ 3 FRONT 14 ...

Page 17: ...SCHEMATIC DIAGRAM _ 4 CD 1 2 CD LOAD CD DRIVE 17 ...

Page 18: ...SCHEMATIC DIAGRAM _ 5 CD 2 2 18 ...

Page 21: ... 21 FL HNA 10SS15T GRID ASSIGNMENT ANODE CONNECTION GRID ASSIGNMENT ANODE CONNECTION ...

Page 22: ... 22 IC BLOCK DIAGRAM ...

Page 23: ... 23 ...

Page 34: ... 34 CD TEST MODE ...