– 31 –

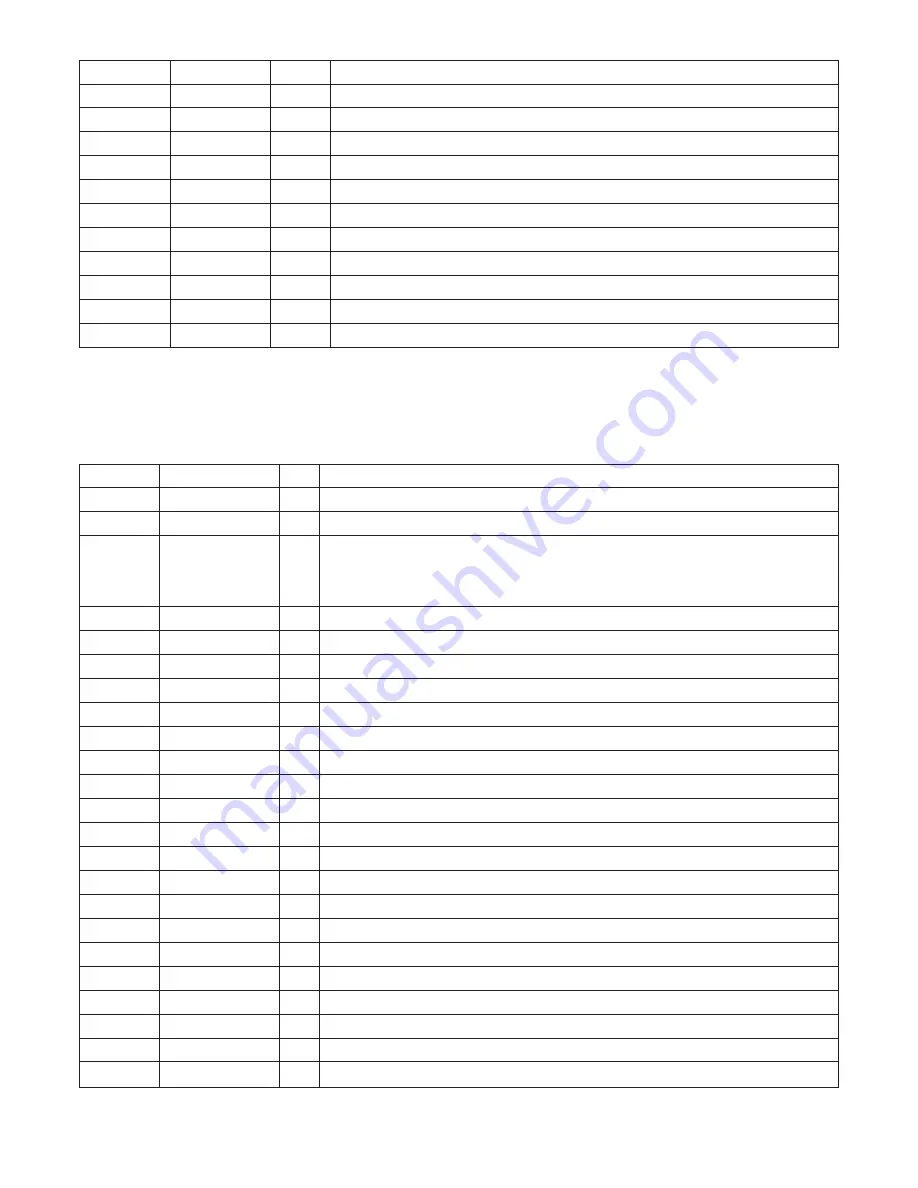

Pin No.

Pin Name

I/O

Description

115

CDG SCK

I

CD-G serial clock input.

116

VSS

–

Ground.

117

HCK

I

Micon interface. (Host clock)

118

VDD3

–

Power supply 3.3V.

119

HD-IN

I

Micon interface. (Host data in)

120

VDD3

–

Power supply 3.3V.

121

HSEL

I

Micon interface. (Host select in)

122

CDG SDATA

I

CD-G data input. (Not used)

123

CDG VFSY

I

CD-G VFSY input. (Not used)

124

CDG SOSI

I

CD-G SOSI input.

125 ~ 128

NC

–

Not connected.

1

NC

–

Not connected.

2

AMUTE

O

Audio analog mute ("H" = Mute ON).

3

FSEQ

I

Synchronization signal detection input pin.

Inputs a high level when the synchronization signal detected from the EFM signal and the

internally generated synchronization signal agree. (Not used)

4

NC

–

Not connected.

5

NC

–

Not connected.

6

EMPH

I

Emphasis input terminal.

7

DATA IN

I

Data input pin.

8

NC

–

Not connected.

9

VSS

–

GND.

10~12

NC

–

Connected to GND.

13

EMERG

I

Power emergency stop (L*3sec = STOP).

14 ~ 19

NC

–

Not connected.

20

XCDRST

O

CD reset output terminal.

21

CMND

O

DATA output pin.

22

CE

O

Chip enable signal output pin.

23

CL

O

Data transfer clock output pin.

24

VSS

–

GND.

25

DRF

I

Focus ON detect pin.

26

WRQ

I

Interruption signal input pin.

27

XBUSY

I/O

READY/BUSY I/O to HOST OD.

28 ~ 30

NC

–

Not connected.

31 ~ 34

TST0 ~ TST3

I/O

Check Land. (Not used)

35

RESET

I

Reset.

IC,

µ

PD78016FGC-574-AB8

Pin No.

Pin Name

I/O

Description

Summary of Contents for NSX-VC8

Page 12: ...SCHEMATIC DIAGRAM _ 1 MAIN 1 2 AMP SECTION 12 ...

Page 13: ...SCHEMATIC DIAGRAM _ 2 MAIN 2 2 TUNER SECTION 13 ...

Page 14: ...SCHEMATIC DIAGRAM _ 3 FRONT 14 ...

Page 17: ...SCHEMATIC DIAGRAM _ 4 CD 1 2 CD LOAD CD DRIVE 17 ...

Page 18: ...SCHEMATIC DIAGRAM _ 5 CD 2 2 18 ...

Page 21: ... 21 FL HNA 10SS15T GRID ASSIGNMENT ANODE CONNECTION GRID ASSIGNMENT ANODE CONNECTION ...

Page 22: ... 22 IC BLOCK DIAGRAM ...

Page 23: ... 23 ...

Page 34: ... 34 CD TEST MODE ...