70

1

2

3

4

5

6

7

8

9

10

11

12, 13

14

15

16

17

18

19, 20

21

22

23

24-28

29

30

31

32, 33

34

35

36

37

38

39

40

41

42

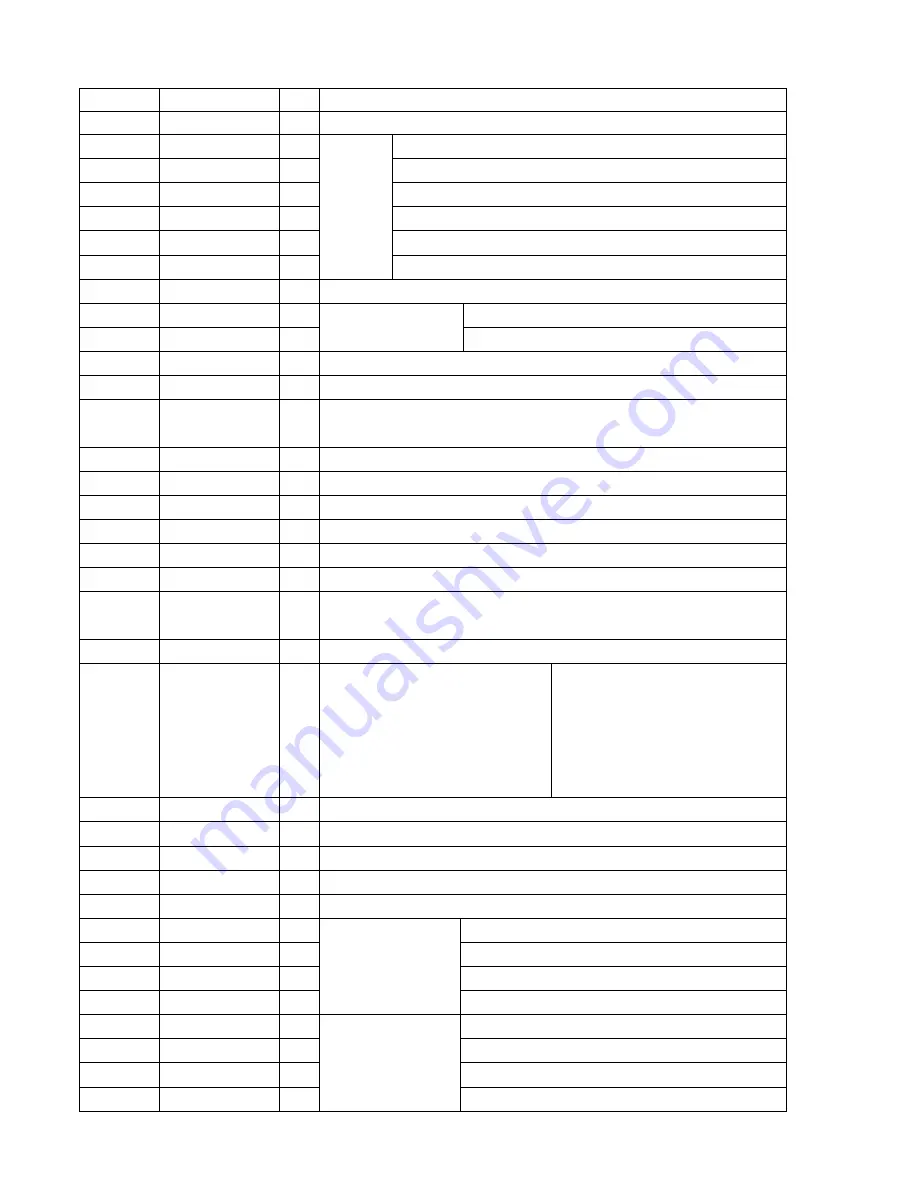

DEFI

TAI

PDO

VVSS

ISET

VVDD

FR

VSS

EFMO

EFMIN

TEST2

CLV+, CLV–

___

V/P

HFL

TES

TOFF

TGL

JP+, JP–

PCK

FSEQ

VDD

SL+ - PUIN

EMPH

C2F

DOUT

TEST3, TEST4

N.C.

MUTEL

LVDD

LCHO

LVSS

RVSS

RCHO

RVDD

MUTER

I

I

O

—

I

—

I

—

O

I

I

O

O

I

I

O

O

O

O

O

—

I/O

O

O

O

I

—

O

—

O

—

—

O

—

O

Defect sense signal (DEF) input pin. (Connect to 0V when not used).

Test signal input pin with built-in pull-down resistor. Be sure to connect to 0V.

Phase comparator output pin to control external VCO.

For PLL.

GND pin for built-in VCO. Be sure to connect to 0V.

Pin to which external resistor adjusting the PD0 output current.

Power supply pin for built-in VCO.

Pin for VCO frequency range adjustment.

Digital system GND. Be sure to connect to 0V.

For slice level control.

EFM signal output pin.

EFM signal input pin.

Test signal input pin with built-in pull-down resistor. Be sure to connect to 0V.

Disc motor control output. Three level output is possible using command.

Rough servo or phase control automatic selection monitoring output pin. Rough servo

at H. Phase servo at L.

Track detect signal input pin. Schmidt input.

Tracking error signal input pin. Schmidt input.

Tracking OFF output pin.

Tracking gain selection output pin. Gain boost at L.

Track jump control signal output pin. Three level output is possible using command.

EFM data playback clock monitoring pin 4.3218 MHz when phase is locked in.

Sync signal detection output pin. H when the sync signal which is detected from EFM

signal and thesync signal which is internally generated agree.

Digital system power supply pin.

The pin is controlled by the serial data

command from microprocessor. When

General purpose input/output pin 1 to 5.

the pin is not used, set the pin to the input

terminal and connect to 0V, or alternately

set the pin to output terminal and leave

the pin open.

De-emphasis monitor output pin. De-emphasis disc is being played back at H.

C2 flag output pin.

DIGITAL OUT output pin. (EIAJ format).

Test signal input pin with built-in pull-down resistor. Be sure to connect to 0V.

Not used. Set the pin to open.

L-channel mute output pin.

L-channel 1-bit DAC.

L-channel power supply pin.

L-channel output pin.

L-channel GND. Be sure to connect to 0V.

R-channel GND. Be sure to connect to 0V.

R-channel 1-bit DAC.

R-channel output pin.

R-channel power supply pin.

R-channel mute output pin.

IC, LC78622ED

Pin No.

Pin Name

I/O

Description

Summary of Contents for XR-MD200

Page 6: ...6 DISASSEMBLY INSTRUCTIONS 1 Remove the two screws 2 Remove the two screws 1 2 ...

Page 13: ...14 13 BLOCK DIAGRAM IC301 LC866532A ...

Page 14: ...1 2 3 4 5 6 7 8 9 10 11 12 13 14 A B C D E F G H I J K 16 15 WIRING 1 POWER AMP AC 230V 50Hz ...

Page 15: ...18 17 SCHEMATIC DIAGRAM 1 POWER AMP Q261 262 MUTE R261 22k R262 22k 220k 220k 1000p 1000p ...

Page 16: ...1 2 3 4 5 6 7 8 9 10 11 12 13 14 A B C D E F G H I J K 20 19 WIRING 2 FRONT ...

Page 17: ...22 21 SCHEMATIC DIAGRAM 2 FRONT IC301 LC866532A 5L31 ...

Page 28: ...40 39 BLOCK DIAGRAM 1 CD ...

Page 29: ...42 41 BLOCK DIAGRAM 2 MD TO MAIN C B CN502 TO CD C B CN6 ...

Page 30: ...44 43 WIRING 1 CD 14 13 12 11 10 9 8 7 6 5 4 3 2 1 A B C D E F G H I J CD C B COMPONENT SIDE ...

Page 31: ...46 45 1 2 3 4 5 6 7 8 9 10 11 12 13 14 A B C D E F G H I J TP3 CD C B CONDUCTOR SIDE ...

Page 32: ...48 47 SCHEMATIC DIAGRAM 1 CD 1 2 DTC114TK ...

Page 33: ...50 49 SCHEMATIC DIAGRAM 2 CD 2 2 RESET 5M36 ...

Page 34: ...1 2 3 4 5 6 7 8 9 10 11 12 13 14 A B C D E F G H I J K 52 51 WIRING 2 FUNCTION ...

Page 35: ...54 53 SCHEMATIC DIAGRAM 3 FUNCTION ...

Page 59: ...81 IC BA5936 Rog CURRENT DETECTOR TERMINAL IC BA5970FP IC BA6417F ...

Page 60: ...82 IC BD7910FV IC AK4519VF ...

Page 72: ...931196 Printed in Singapore 2 11 IKENOHATA 1 CHOME TAITO KU TOKYO 110 JAPAN TEL 03 3827 3111 ...