– 48 –

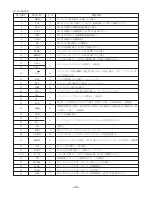

1

I-STEREO/I-DRF

I

During TU FUNC, tuner stereo signal input / during CD FUNC, CD ASP IC DRF data input.

2

O-BEEP

O

Buzzer control.

3

I-RDSDATA/

I/O

During TU FUNC, RDS serial data input (EZ only) / during CD FUNC, CD DSP IC command in

O-CD-CE

data output.

4

I-TUDO/I-SUBQ

I

During TU FUNC, tuner IF count serial data input / during CD FUNC, CD DSP IC subcode data

input.

5

O-MSTB

O

Main IC control serial strobe output.

6

O-CLK

O

IC control serial clock output.

7

O-DATA

O

IC control serial data output.

8

O-FUNCCE

O

FUNC IC control chip enable output.

9

O-PLL-CE

O

Tuner PLL IC control chip enable output.

10

O-CLK-SIFT

O

Micon clock shift control output. L : shift up (initial H)

11

RST

I

Reset input.

12

I-HOLD (A/D)

I

Power failure overcharge detection input.

13

I-TU-SIG/

I

During TU FUNC, tuner signal level input / during TAPE FUNC, music sensor detection input.

I-MS (A/D)

14

VSS1

-

GND.

15

CF1

I

Oscillator input for system clock (9.43MHz).

16

CF2

O

Oscillator output for system clock (9.43MHz).

17

VDD1

-

Power supply.

18

I-ENC2 (A/D)

I

Waveform input for MD jog rotary encoder.

19

I-KEY1 (A/D)

I

Tact key A/D level input.

20

I-KEY0 (A/D)

I

Tact key A/D level input.

21

I-DSW (A/D)

I

CD deck RECA, B, CST switch detection input.

22

I-CDTSW (A/D)

I

CD mecha switch detection input.

23

I-ENC1 (A/D)

I

Waveform input for jog rotary encoder.

24

I-ENC0 (A/D)

I

Waveform input for volume rotary encoder.

25

I-LEVEL (A/D)

I

Audio signal level detection input (for level bar, CD blank skip).

26

I-SC/I-MIC (A/D)

I

CD serial clock input / mic level detection input.

27

I-TMBASE

I

Reference signal input for clock.

28

I-RDSCLK/

I

During TU FUNC, RDS serial clock input (EZ only) / during CD FUNC, CD DSP IC WRQ

I-WRQ

input.

29

I-RMC

I

Remote control signal input.

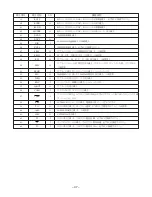

30 ~ 42

G13 ~ G1

O

FL grid output.

43 ~ 45

P35 ~ P33

O

FL segment output.

46

VDD3

-

Power supply.

47 ~ 50

P32 ~ P29

O

FL segment output.

51

VP

-

Power supply for FL input.

52 ~ 62

P28 ~ P18

O

FL segment output.

63

MD/P17

I/O

No MD setting switch input (not used) / FL segment output.

64

ECO OFF/P16

I/O

ECO off setting switch input / FL segment output.

65

P-DEMO/P15

I/O

Demo with panel setting switch input (not used) / FL segment output.

IC DESCRIPTION

IC, LC87F65C8AU : ACJ-4

Pin No.

Pin Name

I/O

Description

Summary of Contents for XR-MD510

Page 5: ... 5 ...

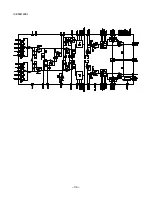

Page 15: ... 15 SCHEMATIC DIAGRAM 1 MAIN PT1 PT2 RELAY ...

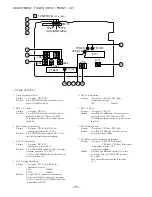

Page 17: ... 17 SCHEMATIC DIAGRAM 2 FRONT SW 1 SW 2 FACE A FACE B FACE C DECK ...

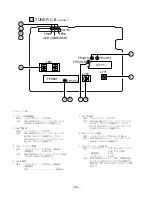

Page 20: ... 20 SCHEMATIC DIAGRAM 3 CD CD LOAD CD DRIVE ...

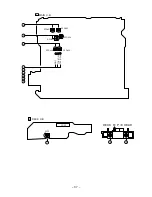

Page 22: ... 22 SCHEMATIC DIAGRAM 4 D TUNER ...

Page 24: ... 24 SCHEMATIC DIAGRAM 5 K TUNER ...

Page 26: ... 26 SCHEMATIC DIAGRAM 6 EZ TUNER ...

Page 29: ... 29 IC BLOCK DIAGRAM IC BA5936S IC BU2099FV ...

Page 30: ... 30 IC BU2092F IC BU1920FS ...

Page 31: ... 31 IC MM1454XFBE IC LA1837NL ...

Page 32: ... 32 IC TA2040AF IC HA12211 ...

Page 33: ... 33 IC CXA1553P IC LC72131D ...

Page 34: ... 34 IC BD3876KS2 ...

Page 38: ... 38 8 SFR130 TP3 VREF TP2 FE C CD C B L201 7 TP1 K SCAN GND IC201 7 B FRONT C B ...

Page 43: ... 43 98 O ARDY O 99 O SREQ O 100 I MREQ I ja ja 01234 ja 0123 fLl ...

Page 55: ... 55 FL 13 ST 44GNK ACJ 4 GRID ASSIGNMENT ANODE CONNECTION GRID ASSIGNMENT ...

Page 56: ... 56 ANODE CONNECTION ...