– 54 –

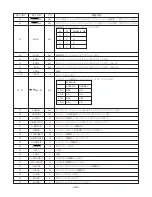

38

LVSS

–

Left channel one-bit D/A converter ground. Must be connected to 0V.

39

RVSS

–

Right channel one-bit D/A converter ground. Must be connected to 0V.

40

RCHO

O

Right channel one-bit D/A converter output.

41

RVDD

–

Right channel one-bit D/A converter power supply.

42

MUTER

O

Right channel one-bit D/A converter mute ouput. (Not used)

43

XVDD

–

Crystal oscillator power supply.

44

XOUT

O

Connections for a 16.934MHz crystal oscillator element.

45

XIN

I

46

XVSS

–

Crystal oscillator ground. Must be connected to 0V.

47

SBSY

O

Subcode block synchronization signal output. (Not used)

48

EFLG

O

C1, C2 single and double error correction monitor pin. (Not used)

49

PW

O

Subcode P, Q, R, S, T, U, V and W output. (Not used)

50

SFSY

O

Subcode frame synchronization signal output. This signal falls when the subcode are in

the standby state. (Not used)

51

SBCK

I

Subcode readout clock input. This is a Schmitt input.

(Must be connected to 0V when unused)

52

FSX

O

Output for the 7.35 kHz synchronization signal divided from the crystal oscillator.

(Not used)

53

WRQ

O

Subcode Q output standby output.

54

RWC

I

Readwrite control input. This is a Schmitt input.

55

SQOUT

O

Subcode Q output.

56

COIN

I

Command input from the control microprocessor.

57

CQCK

I

Input for both the command input acquisition clock and the SQOUT pin subcode

readout clock input. This is a Schmitt input.

58

RES

I

Chip reset pin. This pin must be set low briefly after power is first applied.

59

T11

O

Test output. Leave open. (Normally outputs a low level). (Not used)

60

16M

O

16.9344 MHz output. (Not used)

61

4.2M

O

4.2336 MHz output.

62

T5

I

Test input. A pull-down resistor is built in. Must be connected to 0V.

63

CS

I

Chip select input. A pull-down resistor is built in. Must be connected to 0V if not

controlled.

64

T1

I

Test input. No pull-down resistor. Must be connected to 0V.

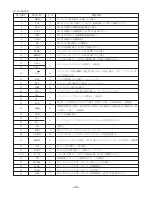

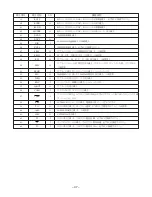

Pin No.

Pin Name

I/O

Description

Summary of Contents for XR-MD510

Page 5: ... 5 ...

Page 15: ... 15 SCHEMATIC DIAGRAM 1 MAIN PT1 PT2 RELAY ...

Page 17: ... 17 SCHEMATIC DIAGRAM 2 FRONT SW 1 SW 2 FACE A FACE B FACE C DECK ...

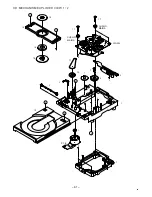

Page 20: ... 20 SCHEMATIC DIAGRAM 3 CD CD LOAD CD DRIVE ...

Page 22: ... 22 SCHEMATIC DIAGRAM 4 D TUNER ...

Page 24: ... 24 SCHEMATIC DIAGRAM 5 K TUNER ...

Page 26: ... 26 SCHEMATIC DIAGRAM 6 EZ TUNER ...

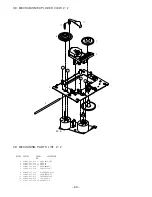

Page 29: ... 29 IC BLOCK DIAGRAM IC BA5936S IC BU2099FV ...

Page 30: ... 30 IC BU2092F IC BU1920FS ...

Page 31: ... 31 IC MM1454XFBE IC LA1837NL ...

Page 32: ... 32 IC TA2040AF IC HA12211 ...

Page 33: ... 33 IC CXA1553P IC LC72131D ...

Page 34: ... 34 IC BD3876KS2 ...

Page 38: ... 38 8 SFR130 TP3 VREF TP2 FE C CD C B L201 7 TP1 K SCAN GND IC201 7 B FRONT C B ...

Page 43: ... 43 98 O ARDY O 99 O SREQ O 100 I MREQ I ja ja 01234 ja 0123 fLl ...

Page 55: ... 55 FL 13 ST 44GNK ACJ 4 GRID ASSIGNMENT ANODE CONNECTION GRID ASSIGNMENT ...

Page 56: ... 56 ANODE CONNECTION ...