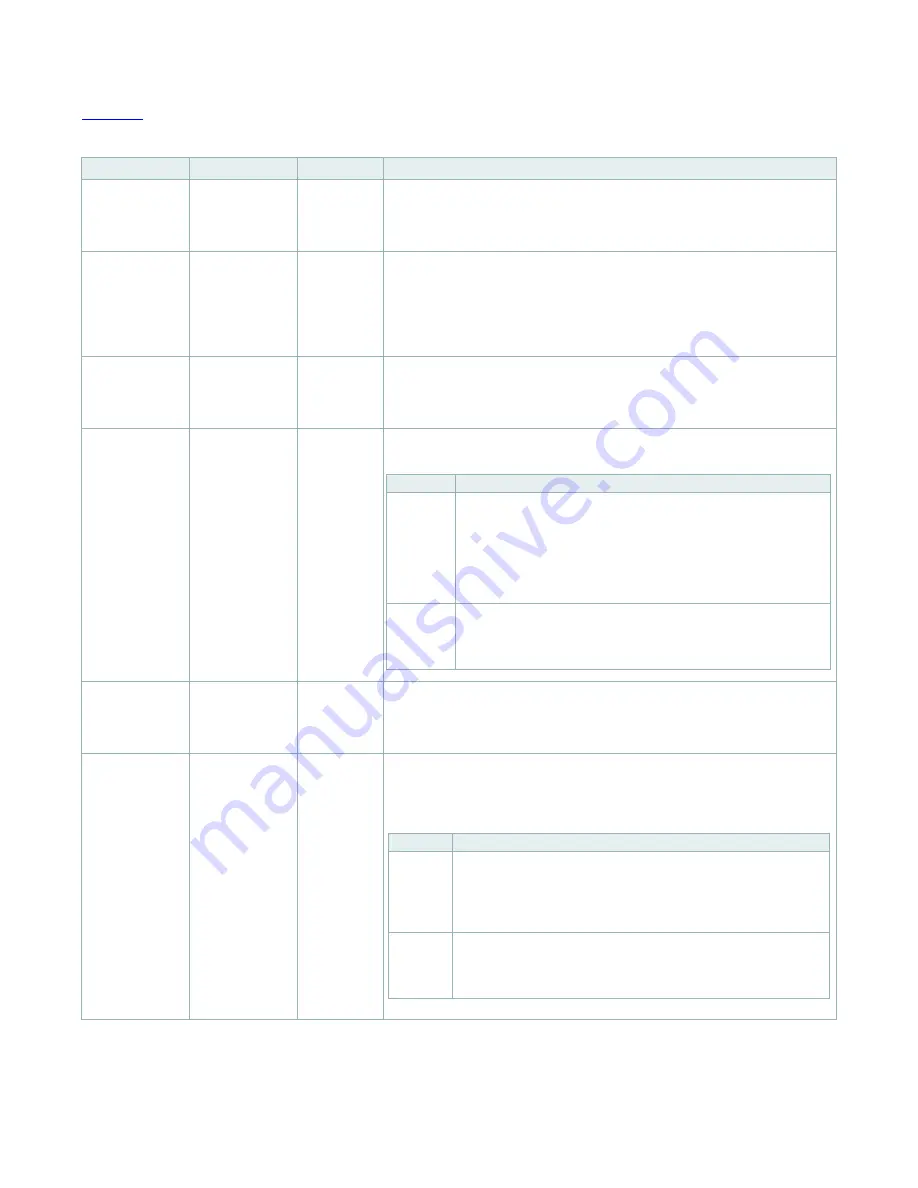

Pinout Information

Pin Descriptions

Table 2-2

provides detailed Graphics Port pin descriptions.

Table 2-2 Graphics Port Pin Descriptions

Name

Pin(s)

Type

Function

GCLK

31

ID 5

GPort Pixel Clock. The GCLK pin is used for graphics port image

capture. The polarity can be selected by the GCKPOL bit.The GCLK

input can be disabled by the GCLKOFF bit to reduce power

consumption.

GVS

32

ID 5

GPort Vertical Sync. Indicates start of next field or frame of data. This

signal is internally polarity corrected so GVS can be either active-high or

active-low. The current status of the GVS signal is given by VPOL and

VSOK status bits when the graphics port is selected by the PORTSEL bit.

GVS is not used when a composite digital sync source is used which can

be specified by the SOGSEL and COMPEN bits.

GPEN

34

ID 5

GPort Pixel Enable. Used when external flow control capture mode is

enabled by the EXTFCE bit. When GPEN is active, the input data is valid.

The polarity can be selected by the GPENPOL bit. Use of this pin allows

non-contiguous input data.

GHSSOG

33

ID 5

GPort Horizontal Sync/GPort Sync-on-Green. This pin has two different

functions depending on the SOGSEL bit:

GCOAST

36

OS

GPort PLL Coast. Tells the PLL when to coast (ignore GREF) during

vertical blanking. Used to prevent the PLL from reacting to extra or missing

HS pulses during vertical blanking. Coast duration and polarity is

programmable through the PLLCM, PLLCB & PLLCE bits.

GFBK

35

ID 5

GPort PLL Feedback / Line Advance Input.

• When PORTSEL=0, this pin is not used.

• When PORTSEL=1, this pin has two different functions depending on the

EXTFCE bit:

SOGSEL

GHSSOG Function

0

GHS: GPort Horizontal Sync. Indicates the start of the next line of

input data. This signal is internally polarity corrected and monitored

for composite sync content. The current status of the GHS signal is

given by the HPOL, HSOK & COMP status bits when the graphics

port is selected by the PORTSEL bit. GHS can supply horizontal

sync information or digital composite sync information depending on

the COMPEN and SOGSEL bits.

1

SOG: Pin is sync-on-green. Driven by an external sync stripper

circuit, this pin is monitored (SOGACT status bit) and can supply

composite sync information (depending on SOGSEL & COMPEN

bits).

EXTFCE

GFBK Function

0

GFBK: An input that is typically driven by the FBK output of an ADC/

PLL device. In free running capture mode this signal is used to define

the horizontal capture region (along with the CAPL and CAPW

registers), and advances the GPort capture controller to the next

input line. The LAVPOL bit is used to select the polarity of GFBK.

1

GLAV: An input to the graphics port line advance. Used in external

flow control capture mode. When GLAV transitions (depending on

LAVPOL and LAVMOD bits), the GPort capture controller advances

to the next input line.

Summary of Contents for LCT2662

Page 25: ......

Page 26: ......

Page 27: ......

Page 28: ......

Page 29: ......

Page 30: ......

Page 31: ......

Page 32: ......

Page 33: ......

Page 34: ......

Page 94: ......

Page 95: ......

Page 96: ......

Page 97: ......

Page 98: ......

Page 99: ......

Page 100: ......

Page 101: ......

Page 102: ......

Page 103: ...Input configuration Power amplifier ...

Page 104: ......

Page 105: ......

Page 106: ......

Page 107: ......

Page 108: ......

Page 109: ......

Page 110: ......

Page 111: ...Exploded View Diagram Exploded View Diagram ...