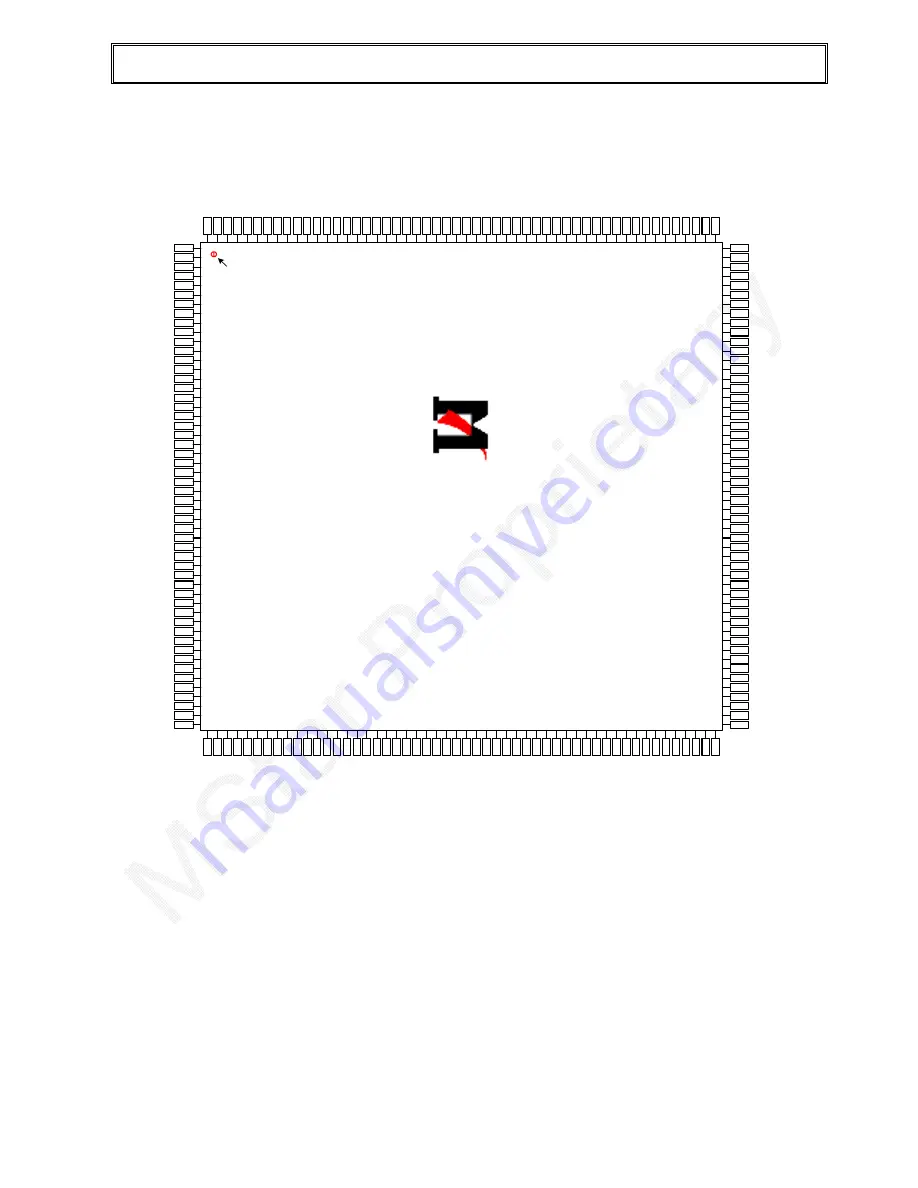

PIN DIAGRAM (MST5151A)

Pin 1

1

2

3

4

5

7

9

11

13

14

17

18

21

23

25

27

28

30

32

34

36

39

41

43

6

8

10

12

15

16

19

20

22

24

26

29

31

33

35

37

38

40

42

44

45

46

47

48

50

51

52

49

53

54

55

56

57

59

61

63

65

66

69

70

73

75

77

79

80

82

84

86

88

91

93

95

58

60

62

64

67

68

71

72

74

76

78

81

83

85

87

89

90

92

94

96

97

98

99

10

0

10

2

10

3

10

4

10

1

20

8

20

7

20

6

20

5

20

4

20

2

20

0

19

8

19

6

19

5

19

2

19

1

18

8

18

6

18

4

18

2

18

1

17

9

17

7

17

5

17

3

17

0

16

8

16

6

20

3

20

1

19

9

19

7

19

4

19

3

19

0

18

9

18

7

18

5

18

3

18

0

17

8

17

6

17

4

17

2

17

1

16

9

16

7

16

5

16

4

16

3

16

2

16

1

15

9

15

8

15

7

16

0

156

155

154

153

152

150

148

146

144

143

140

139

136

134

132

130

129

127

125

123

121

118

116

114

151

149

147

145

142

141

138

137

135

133

131

128

126

124

122

120

119

117

115

113

112

111

110

109

107

106

105

108

MVR

EF

GN

D

VDDM

MS

T5151A

XXXXX

XXX

XXX

XXXXX

GN

D

AV

DD_M

PL

L

XI

N

XO

U

T

PW

M1

PW

M0

AI

WS

AI

SC

K

VD

D

C

SP

D

IF

O

AU

WS

AU

SD

LV

B0M

VD

D

C

GN

D

VD

D

P

AI

SD

AI

MCK

GN

D

AU

MU

TE

AU

SC

K

AU

MCK

LV

B0P

GN

D

LV

B1M

LV

B1P

LV

B2M

LV

B2P

LV

BC

KM

LV

BC

KP

LV

B3M

LV

B3P

VD

D

C

GN

D

LV

A

0M

LV

A

0P

LV

A

1M

LV

A

1P

LV

A

2M

LV

A

2P

LV

A

CKM

LV

A

CKP

GN

D

VD

D

P

LV

A

3M

LV

A

3P

GN

D

BY

PA

SS

GN

D

DV

I_

R

-

DV

I_

R

+

GN

D

GND

DVI_G+

DVI_G-

AVDD_DVI

DVI_B+

AVDD_DVI

AVDD_PLL

DDCD_DA

GND

HSYNC1

BIN1P

BIN1M

DVI_B-

GND

DVI_CK-

REXT

GND

DDCD_CK

AVDD_ADC

VYSNC1

SOGIN1

GIN1P

GIN1M

RIN1P

RIN1M

BIN0M

BIN0P

GIN0M

GIN0P

SOGIN0

RIN0M

RIN0P

AVDD_ADC

GND

HSYNC0

VSYNC0

RMID

REFP

REFM

VI_DATA[8]

VI_DATA[9]

VI_DATA[10]

VI_DATA[11]

VI_DATA[12]

VI_DATA[13]

VI_DATA[14]

VI_DATA[15]

AVDD_APLL

GPO[5]

GPO[4]

GND

VI

_C

K

VI

_D

AT

A[

0]

VI

_D

AT

A[

1]

VI

_D

AT

A[

2]

VI

_D

AT

A[

3]

VI

_D

AT

A[

4]

VI

_D

AT

A[

7]

GN

D

VDDP

IN

T

RD

Z

DBUS

[0

]

DBUS

[1

]

VI

_D

AT

A[

5]

VI

_D

AT

A[

6]

V

DDC

GN

D

HW

R

ES

ET

AL

E

WR

Z

DBUS

[2

]

DBUS

[3

]

GP

O

[3

]

GP

O

[2

]

GP

O

[1

]

V

DDC

GN

D

MD

AT

A[

31

]

MD

AT

A[

30

]

MD

AT

A[

29

]

MD

AT

A[

28

]

VDDM

GN

D

MD

AT

A[

27

]

MD

AT

A[

26

]

MD

AT

A[

25

]

MD

AT

A[

24

]

MD

AT

A[

23

]

MD

AT

A[

22

]

MD

AT

A[

21

]

M

D

AT

A[

20

]

M

D

AT

A[

19

]

M

D

AT

A[

18

]

M

D

AT

A[

17

]

MD

AT

A[

16

]

DQ

S[

2]

VCT

R

L

DQ

S[

3]

DQ

M

[1

]

DQS[0]

MDATA[0]

GND

VDDC

MADR[10]

MADR[9]

MADR[8]

GND

VDDM

MADR[7]

MADR[6]

MADR[5]

MADR[4]

MADR[3]

MADR[2]

MADR[1]

MADR[0]

WEZ

CASZ

GND

VDDM

RASZ

BADR[0]

BADR[1]

AVDD_PLL2

GND

MCLK

MCLKZ

MCLKE

MDATA[1]

MDATA[2]

MDATA[3]

MDATA[4]

MDATA[5]

MDATA[6]

MDATA[7]

MDATA[8]

MDATA[9]

MDATA[10]

MDATA[11]

GND

VDDM

MDATA[12]

MDATA[13]

MDATA[14]

MDATA[15]

DQS[1]

DQM[0]

MADR[11]

VDDC

GND

VDDM

CIRCUIT DESCRIPTIONS