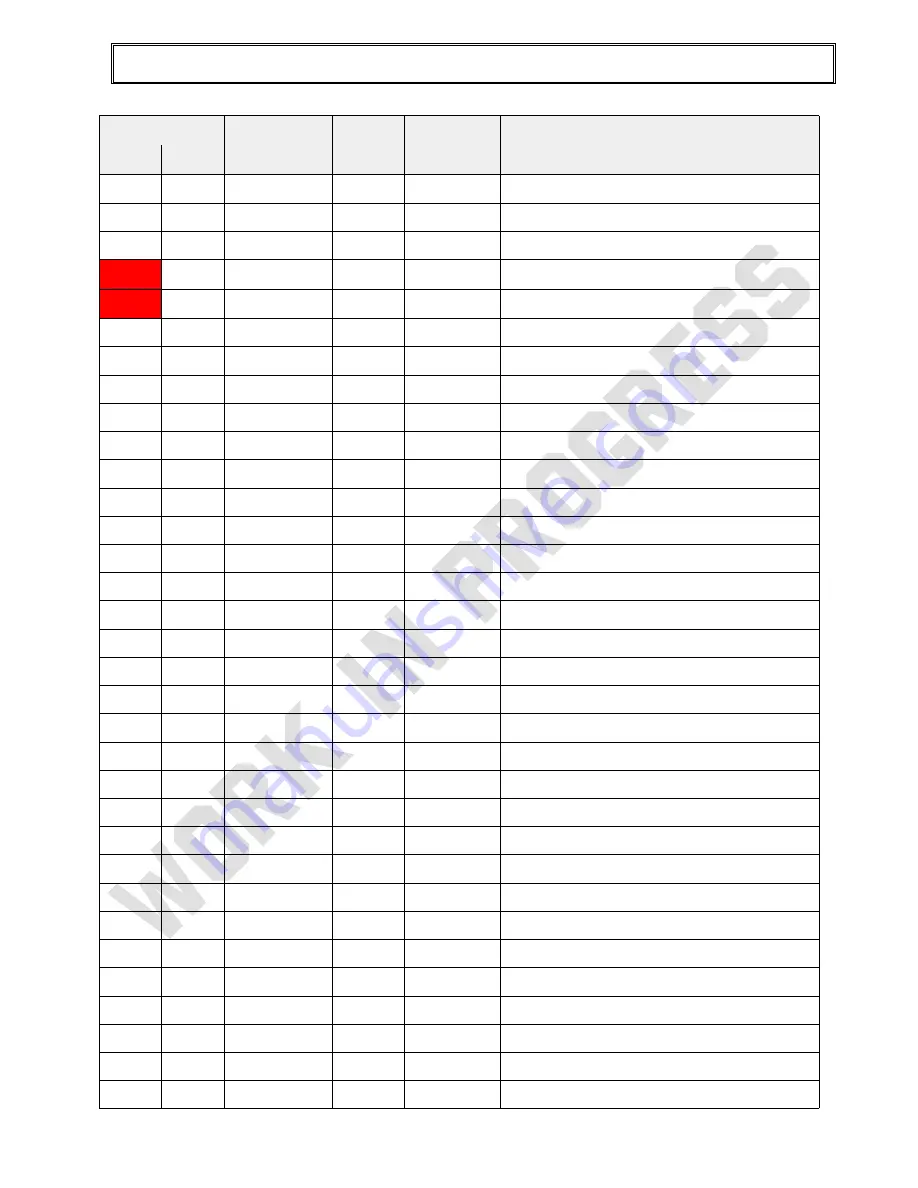

28

11

HFLB

IN

HOUT

Horizontal Flyback Input

29

12

HOUT

OUT

LV

Horizontal Drive Output

30

13

VPROT

IN

GND

Vertical Protection Input

37

PWMV

OUT

LV

PWM Vertical Output

38

DFVBL

OUT

LV

Dynamic Focus Vertical Blanking Output

31

39

SDA

IN/OUT

OBL

I

2

C Bus Data Input/Output

32

40

SCL

IN/OUT

OBL

I

2

C Bus Clock Input/Output

33

41

P21

IN/OUT

LV

Port 2, Bit 1 Input/Output

34

42

P20

IN/OUT

LV

Port 2, Bit 0 Input/Output

35

43

P17

IN/OUT

LV

Port 1, Bit 7 Input/Output

36

44

P16

IN/OUT

LV

Port 1, Bit 6 Input/Output

37

45

P15

IN/OUT

LV

Port 1, Bit 5 Input/Output

38

46

P14

IN/OUT

LV

Port 1, Bit 4 Input/Output

39

47

P13

IN/OUT

LV

Port 1, Bit 3 Input/Output

40

48

P12

IN/OUT

LV

Port 1, Bit 2 Input/Output

41

49

P11

IN/OUT

LV

Port 1, Bit 1 Input/Output

42

50

P10

IN/OUT

LV

Port 1, Bit 0 Input/Output

43

53

VSUP3.3FE

SUPPLY

OBL

Supply Voltage Analog Video Front-end, 3.3 V

44

54

GND

SUPPLY

OBL

Ground Platform

45

55

GND

SUPPLY

OBL

Ground Platform

46

56

VSUP1.8FE

SUPPLY

OBL

Supply Voltage Analog Video Front-end, 1.8 V

47

57

VOUT3

OUT

LV

Analog Video 3 Output

48

58

VOUT2

OUT

LV

Analog Video 2 Output

49

59

VOUT1

OUT

LV

Analog Video 1 Output

50

60

VIN1

IN

GND

Analog Video 1 Input

51

61

VIN2

IN

GND

Analog Video 2 Input

52

62

VIN3

IN

GND

Analog Video 3 Input

53

63

VIN4

IN

GND

Analog Video 4 Input

54

64

VIN5

IN

GND

Analog Video 5 Input

55

65

VIN6

IN

GND

Analog Video 6 Input

56

66

VIN7

IN

GND

Analog Video 7 Input

57

67

VIN8

IN

GND

Analog Video 8 Input

58

68

VIN9

IN

GND

Analog Video 9 Input

Pin No.

Pin Name

Type

Connection

Short Description

PSSDIP

88-pin

PMQFP-2

144-pin

(If not used)

CIRCUIT DESCRIPTIONS