2.1.2. VSP Part

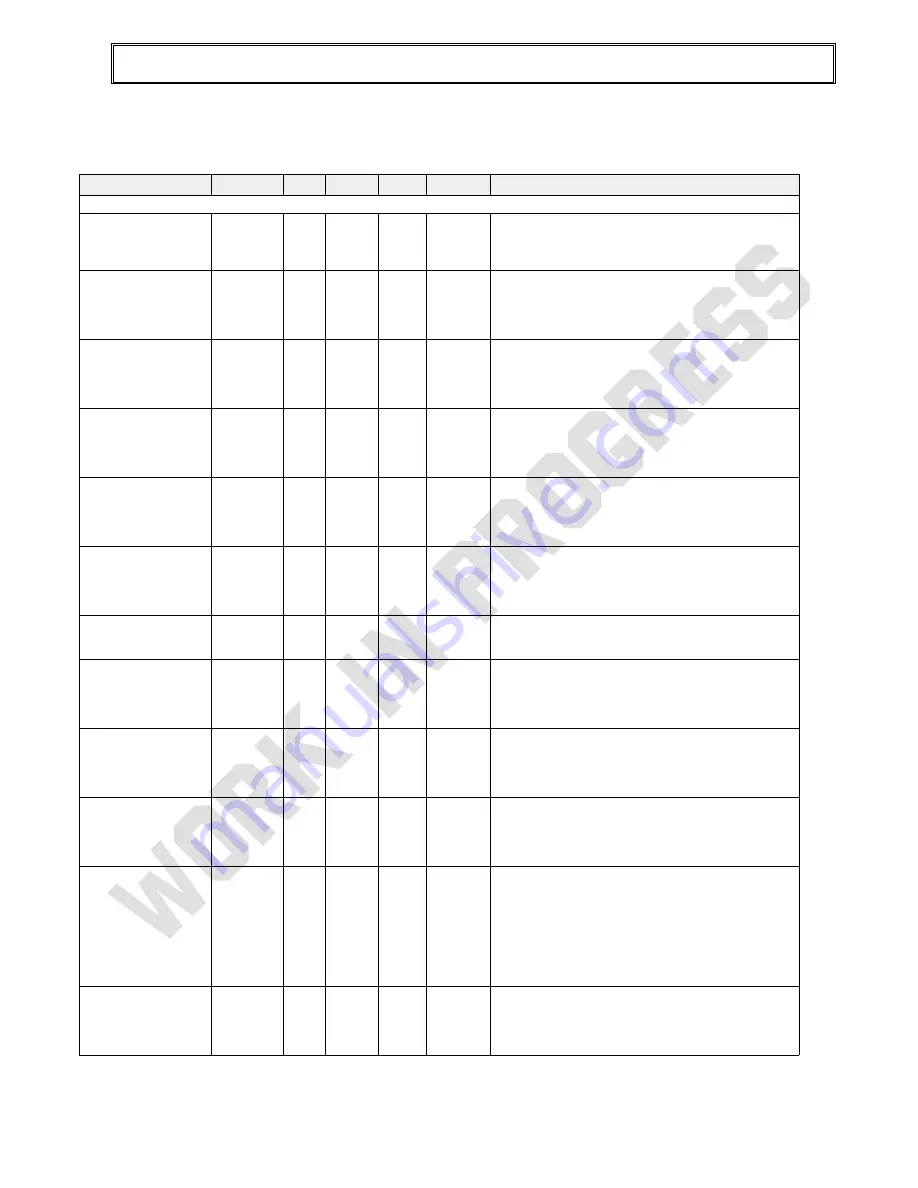

Table 2–5: New VSP Registers

Name

Sub

Dir

Sync

Reset

Range

Function

CD

LPCDEL[2:0]

h07[2:0]

RW

VS_CD

0

-8..7

Window Shift For Fine Error Calculation

100: -4 clock cycles

000: no offset

011: +3 clock cycles

THRSEL[1:0]

h07[13:12]

RW

VS_CD

0

0,1,2,3

H Slicing Level Threshold

00: 50%

01: 31%

10: 37%

11: 25%

CVBSLPBW[1:0]

hB4[5:4]

RW

VS_CD

0

0..3

CVBSLP Bandwidth

00: very small

01: small

10: wide

11: very wide

CVBSFEBW[1:0]

hB4[3:2]

RW

VS_CD

0

0..3

CVBSFE Bandwidth

00: very small

01: small

10: wide

11: very wide

PDTHD[1:0]

hB4[1:0]

RW

VS_CD

0

0,1,2,3

AGC Peak Dark Threshold

00: 140

01: 124

10: 104

11: 70

MINVWIN

hB5[15]

RW

VS_CD

0

0,1

Calculate MINV

0: every line

1: over 4 lines

Note: set to '0' for standard CVBS and '1' for component

input

THRELIM

hB5[14]

RW

VS_CD

0

0,1

Limit Threshold to MINV

0: no limitation

1: limit

CETHD[1:0]

hB5[13:12]

RW

VS_CD

0

0,1,2,3

Coarse Error Threshold

00: +-255

01: +-192

10: +-160

11: +-128

THRELP[1:0]

hB5[11:10]

RW

VS_CD

0

0..3

Lowpass Coeff for Threshold Value

00: very strong

01: strong

10: weak

11: filter off

FECA[1:0]

hB5[4:3]

RW

VS_CD

0

0..3

Fine Error Calculation

00: normal syncs

01: short syncs

10: new algorithm

11: fine error disabled

PWREDLIM[2:0]

hB5[2:0]

RW

VS_CD

0

0..7

Peak White Reduction Limit

000: 63

001: 48

010: 32

011: 24

100: 16

101: 12

110: 8

111: 4

NSREDTHD[1:0]

hB6[1:0]

RW

VS_CD

0

0,1,2,3

Noise Reduction Threshold

00: 256

01: 384

10: 512

11: 640

CIRCUIT DESCRIPTIONS