11

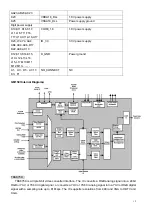

F2

VDDD33_PLL

,

H1 VDDD33_SDDS

J1 VDDD33_DDDS

Digital power supply

G2 VSSD33_PLL

J4 VSSD33_SDDS

K4 VSSD33_DDDS

Digital ground

F4 VDDA33_RPLL

G1 VDDA33_FPLL

H3 VDDA33_SDDS

J3 VDDA33_DDDS

Analog power supply

F3 VSSA33_RPLL

H4 VSSA33_FPLL

H2 VSSA33_DDDS

J2 VSSA33_DDDS

Analog ground

G3

TCLK

Reference clock signal input

K2

ACS_RSET_HD

External resistance port

System Signal

K1 RESETn

Reset

signal

M3

,

M4 IR0

,

IR1

P4

MSTR_SCL

Main clock output signal

P3 MSTR_SDA

Main data output/input signal

信号

R4

EXTCLK

External clock input

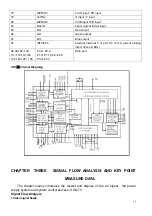

Frame Storage Interface

U24,U23

FSCLKp,FSCLKn

Fine storage clock output

V24,V25 FSRAS,FSCAS

Address

output

V26

FSWE

Write enable port

W26

FSCKE

Read enable port

J24

FSVREF

Reference voltage input

K26

FSVREFVSS

Reference voltage ground

W25

FSVREF

Reference voltage input

W24

FSVREFVSS

Reference voltage ground

L26 FSDQS

Data

filter

F24~F26,G23~G26

H24~H26,J25,J26,

R24~R26,P24~P26

N23~N26,…….

FSDATA31~

FSDATA0

Data input output port

T24,T25,U25,U26 FSDQM3~

FSDQM0

Data output mark

Y26

Y25

FSBKSEL1

,

FSBKSEL0

Layer address

AA24~AA26

AB24~AB26,

AC24~AC26

AD24~AD26

FSADDR11~

FSADDR0

Range address output

E23, F23, H23, J23,

L23,M23,P23, R23,

T23,V23,W23,Y23,

FS_2.5

2.5V power supply