A

A

B

B

C

C

D

D

E

E

E

E

D

D

C

C

B

B

A

A

L

H

DIF0

DIF1

DIF2

OCKS0

OCKS1

CM0

TEST3

XTALE

DMCK

M/S

DIR

A

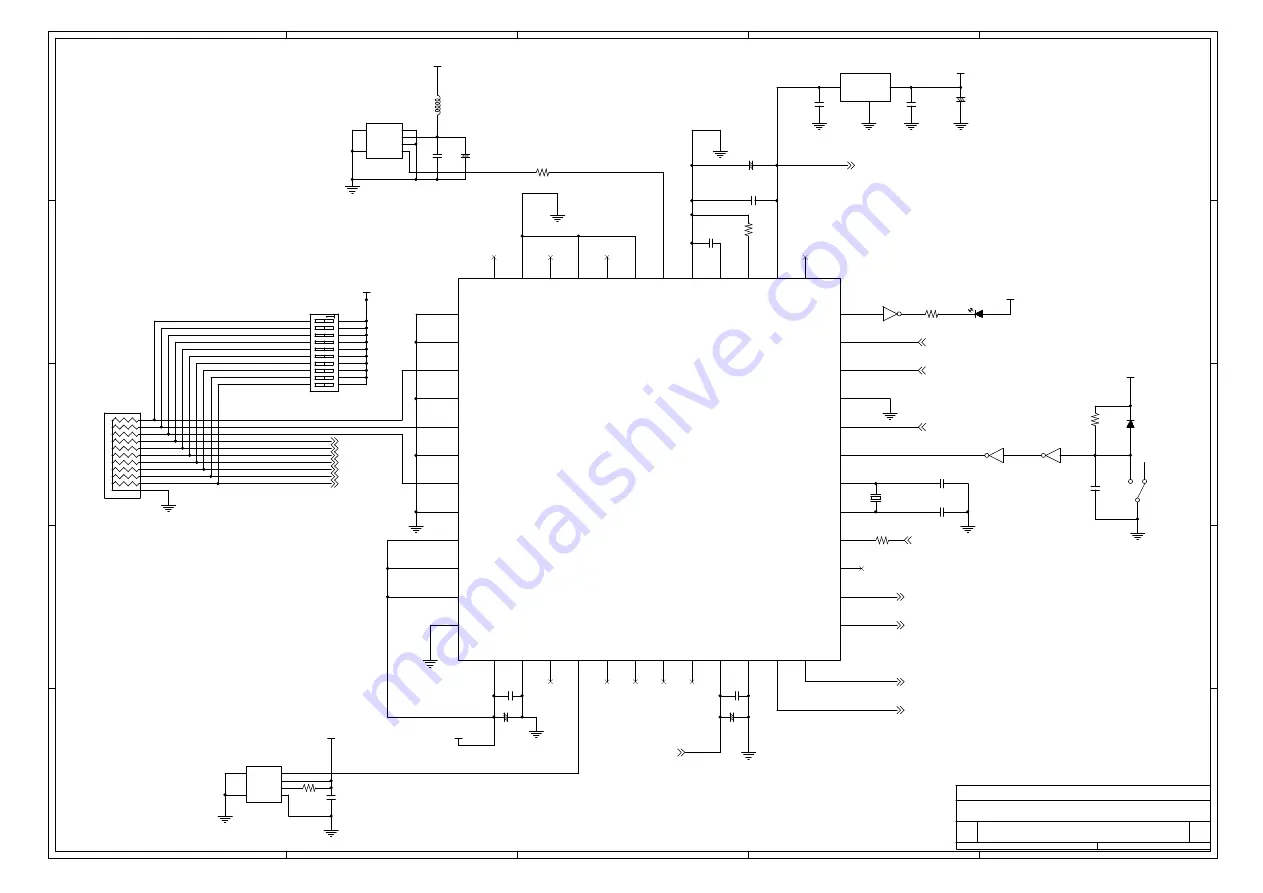

AKD4584

A3

2

4

Tuesday, May 22, 2001

Title

Size

Document Number

Rev

Date:

Sheet

of

OCKS0

OCKS1

CM0

TEST3

XTALE

DMCK

M/S

OCKS0

OCKS1

CM0

DAUX

DIR_SDTI

DIR_BICK

DIR_LRCK

DIR_MCLK

VD

VD

VCC

VCC

VCC

VCC

VCC

VCC

VCC

+ C20

10u

U3C

74HCT04

5

6

C18

0.1u

C23

0.47u

C17

0.1u

R11

1k

R12

10k

SW2

MODE

1

2

3

4

5

6

7

8

9

20

19

18

17

16

15

14

13

12

10

11

L3

47u

1

2

U1C

74HC14

5

6

T1

TO92

2

3

1

VIN

VOUT

GND

PORT1

DIR

1

3

4

2

6

5

OUT

VCC

GND

GND

6

5

PORT2

DIT

1

2

3

4

5

6

GND

IF

VCC

IN

5

6

+

C29

10u

R13

51

C26

5p

C22

0.1u

C27

0.1u

C28

0.1u

R14

1k

+

C21

10u

LED3

ERF

2

1

C19

0.1u

RP3

47k

1

2

3

4

5

6

7

8

9

10

11

C25

0.1u

X2

11.2896MHz

1

2

U1D

74HC14

9

8

C24

5p

R9

470

SW3

DIR

2

1

3

C31

0.1u

U5

AK4114

1

2

3

4

5

6

7

8

9

10

11

13

14

15

16

17

18

19

20

21

22

23

26

27

28

29

30

31

32

33

34

35

36

38

39

40

41

42

43

44

45

46

47

48

12

24

25

37

IPS0

NC

DIF0

TEST2

DIF1

NC

DIF2

IPS1

P/SN

XTL0

XTL1

TVDD

DVSS

TX0

TX1

BOUT

COUT

UOUT

VOUT

DVDD

DVSS

MCKO1

BICK

MCKO2

DAUX

XTO

XTI

PDN

CM0

CM1

OCKS1

OCKS0

INT0

AVDD

R

VCOM

AVSS

RX0

NC

RX1

TEST1

RX2

NC

RX3

VIN

LRCK

SDTO

INT1

D2

HSU119

2

1

+

C30

10u

R10

18k

+

C16

47u