5

3. Phase Comparator Circuit

The PLL (IC1) uses the reference frequency, 5 or 6.25kHz. The phase com-

parator in the IC1 compares the phase of the frequency from the VCO with that

of the comparison frequency, 5 or 6.25kHz, which is obtained by the internal

divider in IC1.

4. PLL Loop Filter Circuit

If a phase difference is found in the phase comparison between the reference

frequency and VCO output frequency, the charge pump output (pin 8) of IC1

generates a pulse signal, which is converted to DC voltage by the PLL loop

filter and input to the varicap of the VCO unit for oscillation frequency control.

5. VCO Circuit

A Colpitts oscillation circuit driven by Q1 directly oscillates the desired fre-

quency. The frequency control voltage determined in the CPU (IC9) and PLL

circuit is input to the varicaps (D32 and D34). This change the oscillation fre-

quency, which is amplified by the VCO buffer (Q5) and output from the VCO

unit.

4) CPU and Peripheral Circuits

1. LCD Display Circuit

The CPU turns ON the LCD via segment and common terminals with 1/4 the

duty and 1/3 the bias, at the frame frequency is 112.5Hz.

2. Display Lamp Circuit

When the LAMP key is pressed, “H” is output form pin 50 of CPU (IC9) to the

bases of Q12. Q12 then turn ON and the LEDs (D12 and D17) light.

3. Reset and Backup

When the power form the DC jack or external battery increases from Circuits 0

V to 2.5 or more, “H” level reset signal is output form the reset IC (IC11) to pin

33 of the CPU (IC9), causing the CPU to reset. The reset signal, however,

waits at 100, and does not enter the CPU untilthe CPU clock (X2) has stabi-

lized.

4. S(Signal) Meter Circuit

The DC potential of pin 8 of IC5 is input to pin 1 of the CPU (IC9), converted

from an analog to a digital signal, and displayed as the S-meter signal on the

LCD.

5. DTMF Encoder

The CPU (IC9) is equipped with an internal DTMF encoder. The DTMF signal

is output from pin 10, through R102 and R158 (for level adjust-ment), and then

through the microphone amplifier (IC7), and is sent to the varicap of the VCO

for modulation. At the same time, the monitor-ing tone passes through the AF

circuit and is output form the speaker.6. CTCSS Encoder The CPU (IC9) is

equipped with an internal tone encoder. The tone signal (67.0 to 250.3 Hz) is

output form pin 9 of the CPU to the varicap (D3) of the VCO for modulation.

Summary of Contents for DJ-195

Page 2: ......

Page 11: ...10 3 M5222FP 600C XA0385 Electronic Volume ...

Page 12: ...11 4 TK14521MTL XA0515 IF System ...

Page 14: ...13 8 S 81250SG QD T1 XA0619 Top View 9 S 80845ALMP EA9 T2 XA0620 Voltage Regulator ...

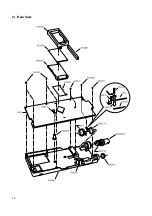

Page 16: ...15 EXPLODED VIEW 1 Front View www ALIMCO ru ...

Page 17: ...16 2 Rear View ...

Page 28: ......

Page 29: ...27 PC BOARD VIEW MAIN SIDE A MAIN Side B ...

Page 30: ...28 SCHEMATIC DIAGRAM ...

Page 31: ...29 BLOCK DIAGRAM www ALIMCO ru ...

Page 32: ......

Page 33: ......