ALINX Xilinx Core Board AC6150 User Manual

12 / 21

Amazon Store: https://www.amazon.com/alinx

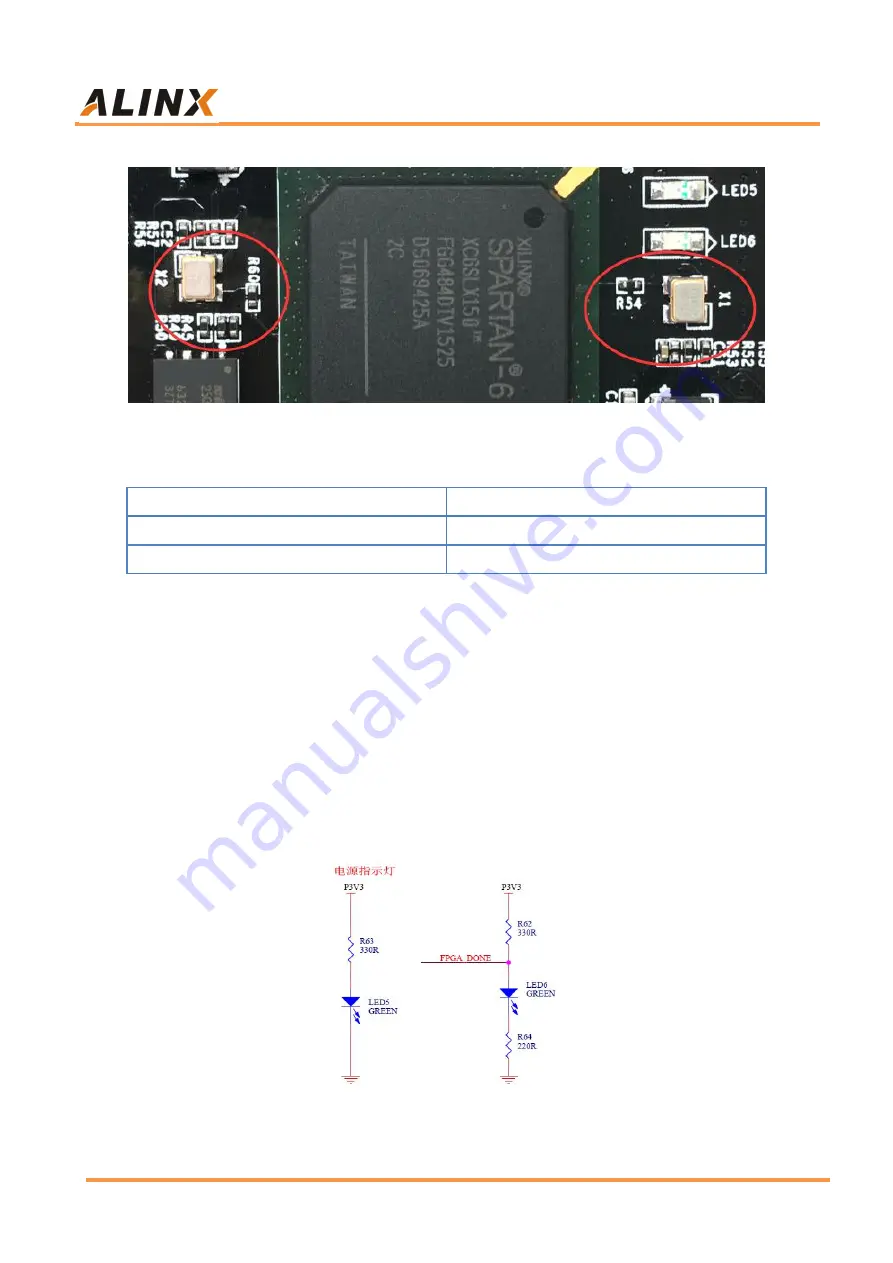

Figure 5-2: Crystal oscillator on the Core Board

Crystal oscillator Pin Assignment

Input Clock

FPGA Pin

50MHz

AB13

27MHz

B10

Part 6: LED Light on Core Board

There are 6 red LED lights on the AC6045 FPGA core board, one of which

is the power indicator light (PWR), one is the configuration LED light (DONE),

and four are the user LED light. When the core board is powered, the power

indicator will illuminate; when the FPGA is configured, the configuration LED

will illuminate.

Figure 6-1: Power Indicator and Configure Indicator schemtaic