ZYNQ Ultr FPGA Board AXU2CGA/B User Manual

11 / 29

Amazon Store: https://www.amazon.com/alinx

PS_DDR4_DQ56

PS_DDR_DQ56_504

J28

PS_DDR4_DQ57

PS_DDR_DQ57_504

K27

PS_DDR4_DQ58

PS_DDR_DQ58_504

H28

PS_DDR4_DQ59

PS_DDR_DQ59_504

H27

PS_DDR4_DQ60

PS_DDR_DQ60_504

G26

PS_DDR4_DQ61

PS_DDR_DQ61_504

G25

PS_DDR4_DQ62

PS_DDR_DQ62_504

K25

PS_DDR4_DQ63

PS_DDR_DQ63_504

J25

PS_DDR4_DM4

PS_DDR_DM4_504

R23

PS_DDR4_DM5

PS_DDR_DM5_504

H23

PS_DDR4_DM6

PS_DDR_DM6_504

L27

PS_DDR4_DM7

PS_DDR_DM7_504

H26

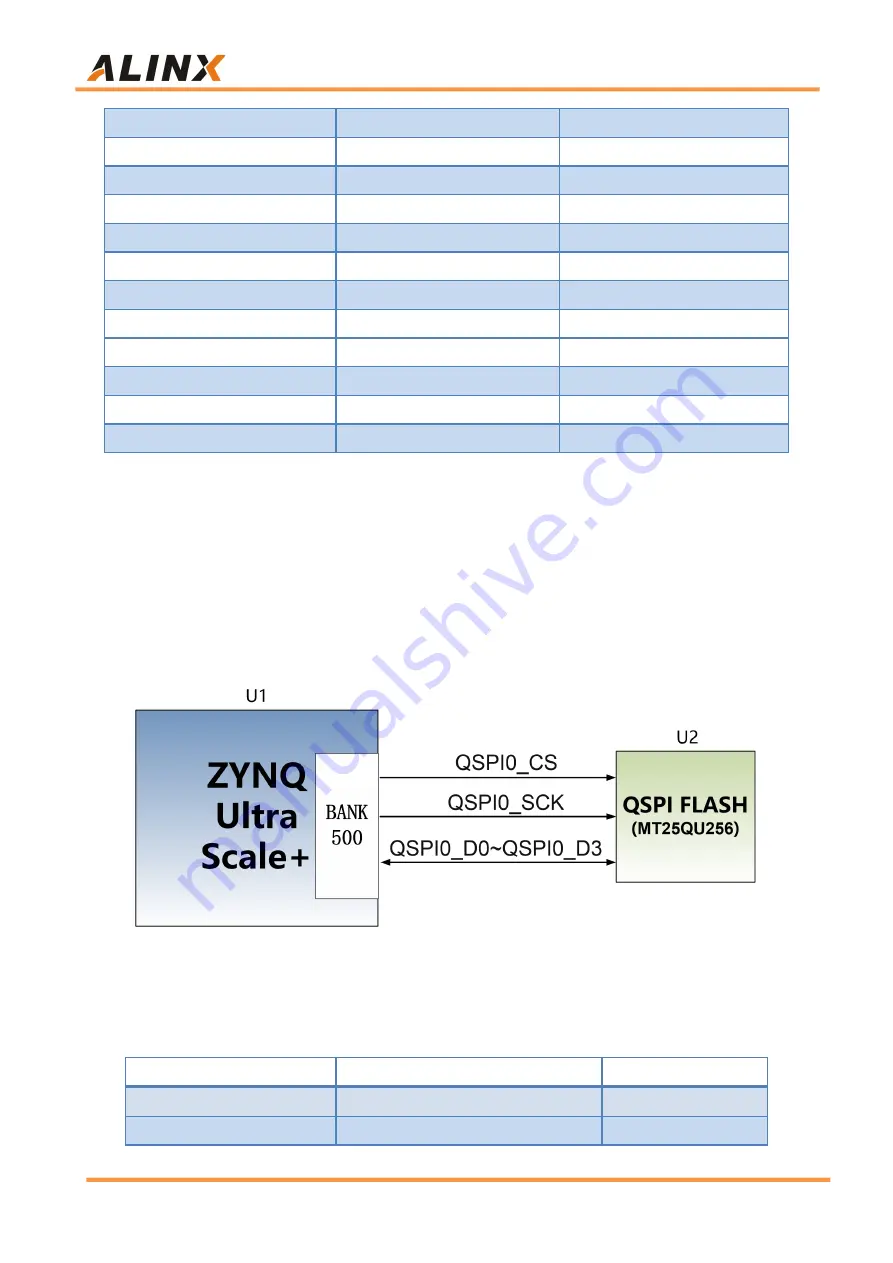

Part 4: QSPI Flash

The AXU2CGA/B board has a 256MBit Quad-SPI FLASH chip, the model

is MT25QU256ABA1EW9-0SIT. QSPI FLASH is connected to the GPIO port of

BANK500 in the PS part of the ZYNQ chip. Figure 4-1 shows the part of QSPI

Flash in the schematic.

Figure 4-1: QSPI Flash

Configure Chip Pin Assignment:

Signal Name

Pin Name

Pin Number

MIO0_QSPI0_SCLK

PS_MIO0_500

AG15

MIO1_QSPI0_IO1

PS_MIO1_500

AG16