Camera interfaces

182

Alvium CSI-2 Cameras User Guide V2.6.2

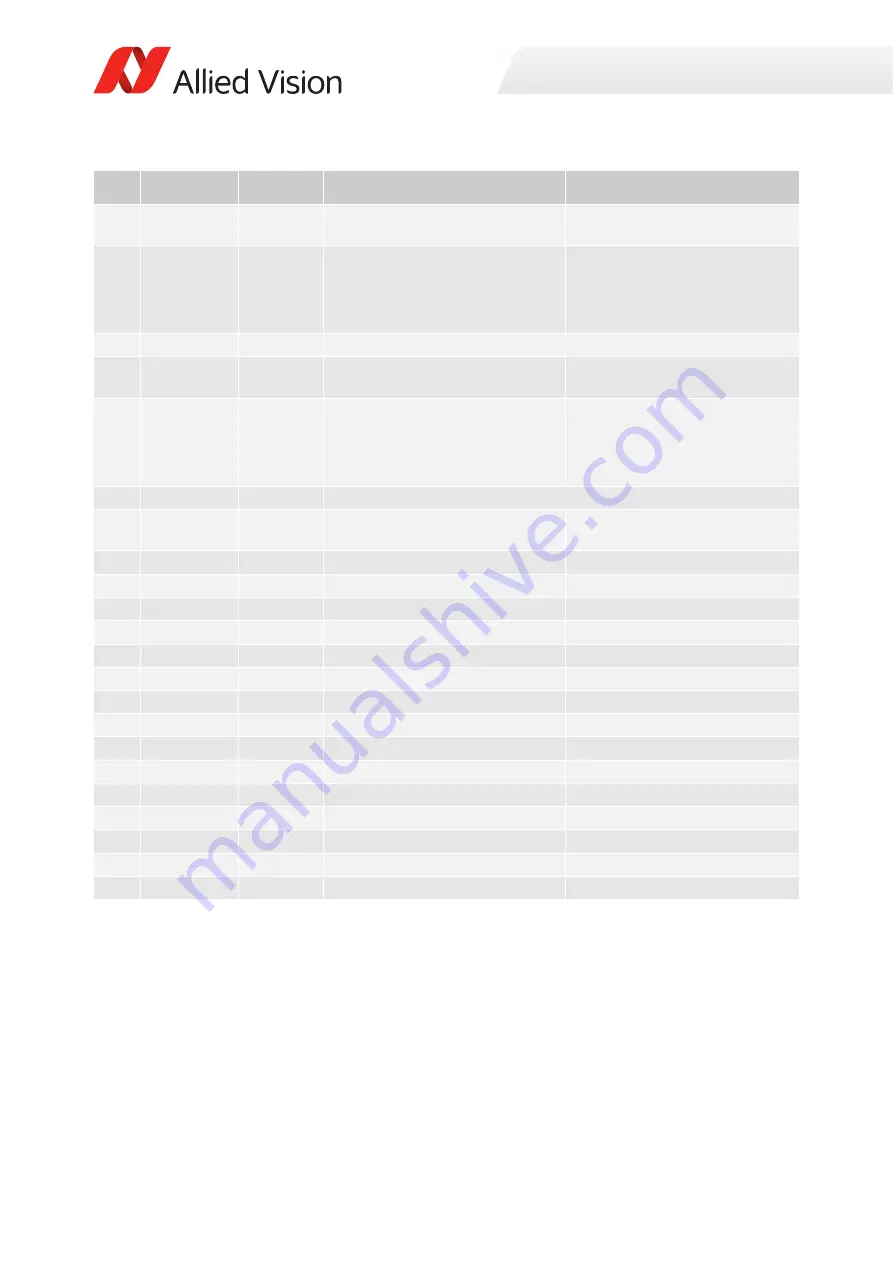

Pin

Signal

Direction

Level

Description

1

VCC-EXT-IN

PWR IN

4.5 to 5.5 VDC

Power supply voltage

Maximum input current: 1.5 A

2

EXT-GPIO 0

IN/OUT

U

in

(low) = -0.3 to 0.8 VDC

U

in

(high) = 2.0 to 5.5 VDC

U

out

(low) = 0 to 0.4 VDC

U

out

(high) = 2.4 to 3.3 VDC at 12 mA

I2C Control

Internal pull-up resistor: 33 to 63 k

Ω

3

EXT-GPIO 1

IN/OUT

See Pin 2, EXT-GPIO 0

4

VCC-EXT-IN

PWR IN

4.5 to 5.5 VDC

Power supply voltage

Maximum input current: 1.5 A

5

EXT-GPIO 2

IN/OUT

U

in

(low) = -0.3 to 0.8 VDC

U

in

(high) = 2.0 to 5.5 VDC

U

out

(low) = 0 to 0.4 VDC

U

out

(high) = 2.4 to 3.3 VDC at 12 mA

GPIO

Internal pull-up resistor: 33 to 63 k

Ω

6

EXT-GPIO 3

IN/OUT

See Pin 5, EXT-GPIO 2

7

VCC-EXT-IN

PWR IN

4.5 to 5.5 VDC

Power supply voltage

Maximum input current: 1.5 A

8

CSI2-TXD3_N

OUT

According to MIPI CSI-2 D-PHY V1.1

CSI-2 TX data lane 3 negative rail

9

CSI2-TXD3_P

OUT

According to MIPI CSI-2 D-PHY V1.1

CSI-2 TX data lane 3 positive rail

10

GND

PWR

0 VDC

Power supply ground

11

CSI2-TXD2_N

OUT

According to MIPI CSI-2 D-PHY V1.1

CSI-2 TX data lane 2 negative rail

12

CSI2-TXD2_P

OUT

According to MIPI CSI-2 D-PHY V1.1

CSI-2 TX data lane 2 positive rail

13

GND

PWR

0 VDC

Power supply ground

14

CSI2-TXC_N

OUT

According to MIPI CSI-2 D-PHY V1.1

CSI-2 TX clock lane negative rail

15

CSI2-TXC_P

OUT

According to MIPI CSI-2 D-PHY V1.1

CSI-2 TX clock lane positive rail

16

GND

PWR

0 VDC

Power supply ground

17

CSI2-TXD1_N

OUT

According to MIPI CSI-2 D-PHY V1.1

CSI-2 TX data lane 1 negative rail

18

CSI2-TXD1_P

OUT

According to MIPI CSI-2 D-PHY V1.1

CSI-2 TX data lane 1 positive rail

19

GND

PWR

0 VDC

Power supply ground

20

CSI2-TXD0_N

OUT

According to MIPI CSI-2 D-PHY V1.1

CSI-2 TX data lane 0 negative rail

21

CSI2-TXD0_P

OUT

According to MIPI CSI-2 D-PHY V1.1

CSI-2 TX data lane 0 positive rail

22

GND

PWR

0 VDC

Power supply ground

Table 89: Camera FPC connector pin assignment