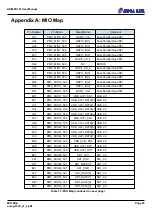

ADM-PA101 User Manual

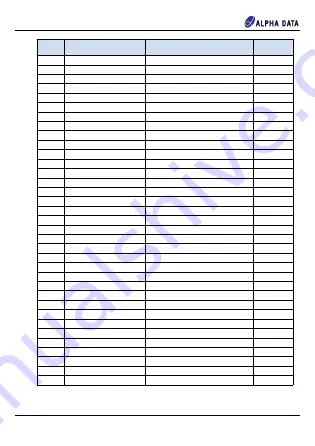

Pin

Number

Signal Name

Pin Name

IO Voltage

J21

FIREFLY_SCL

IO_L8N_406

3.3

J20

FIREFLY_SDA

IO_L8P_406

3.3

C8

FIREFLY_TX0_N

GTY_TXN0_206

MGT

C9

FIREFLY_TX0_P

GTY_TXP0_206

MGT

B10

FIREFLY_TX1_N

GTY_TXN1_206

MGT

B11

FIREFLY_TX1_P

GTY_TXP1_206

MGT

A8

FIREFLY_TX2_N

GTY_TXN2_206

MGT

A9

FIREFLY_TX2_P

GTY_TXP2_206

MGT

A12

FIREFLY_TX3_N

GTY_TXN3_206

MGT

A13

FIREFLY_TX3_P

GTY_TXP3_206

MGT

C18

FPGA_SYSMON_I2C_SCL

PMC_MIO44_501

1.8

A18

FPGA_SYSMON_I2C_SDA

PMC_MIO45_501

1.8

K14

GBTCLK2_PIN_N

GTY_REFCLKN1_202

MGT REFCLK

K15

GBTCLK2_PIN_P

GTY_REFCLKP1_202

MGT REFCLK

H14

GBTCLK3_PIN_N

GTY_REFCLKN1_203

MGT REFCLK

H15

GBTCLK3_PIN_P

GTY_REFCLKP1_203

MGT REFCLK

D14

GBTCLK5_PIN_N

GTY_REFCLKN1_205

MGT REFCLK

D15

GBTCLK5_PIN_P

GTY_REFCLKP1_205

MGT REFCLK

C33

GEM0_MDC

LPD_MIO24_502

3.3

D33

GEM0_MDIO

LPD_MIO25_502

3.3

C19

GEM0_RST_L

PMC_MIO37_501

1.8

B37

GEM0_RX_CLK

LPD_MIO6_502

3.3

D36

GEM0_RX_CTRL

LPD_MIO11_502

3.3

C37

GEM0_RXD_0

LPD_MIO7_502

3.3

E37

GEM0_RXD_1

LPD_MIO8_502

3.3

F37

GEM0_RXD_2

LPD_MIO9_502

3.3

E36

GEM0_RXD_3

LPD_MIO10_502

3.3

A39

GEM0_TX_CLK

LPD_MIO0_502

3.3

A37

GEM0_TX_CTRL

LPD_MIO5_502

3.3

B39

GEM0_TXD_0

LPD_MIO1_502

3.3

C39

GEM0_TXD_1

LPD_MIO2_502

3.3

C38

GEM0_TXD_2

LPD_MIO3_502

3.3

A38

GEM0_TXD_3

LPD_MIO4_502

3.3

AV13

HA00_CC_N

IO_L12N_GC_XCC_N4P1_M2P133_708

FMC_VADJ

AU13

HA00_CC_P

IO_L12P_GC_XCC_N4P0_M2P132_708

FMC_VADJ

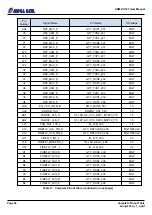

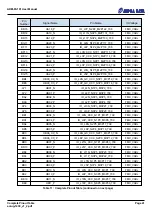

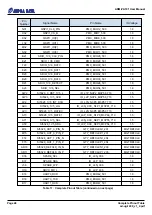

Table 11 : Complete Pinout Table (continued on next page)

Page 39

Complete Pinout Table

ad-ug-1430_v1_2.pdf