ADM-PCIE-8V3 User Manual

Signal

Target FPGA Input

I/O Standard

pin

REFCLK100M

IO_L24P_T3U_N10_EMCCLK_65

LVCMOS18

AJ28

Table 7 : EMCCLK

3.2.4 QSFP28

The QSFP28 cages are located in MGT tiles 129 and 128 and use a 161.1328125MHz default reference clock.

Note that this clock frequency can be changed to any arbitrary clock frequency up to 400MHz by re-programing

the Si5338 reprogrammable clock oscillator via system monitor. This can be done using the Alpha Data API or

over USB with the appropriate Alpha Data Software tools.

Signal

Target FPGA Input

I/O Standard

"P" pin

"N" pin

GTY_CLK_0B

MGTREFCLK0_129

LVDS

N33

N34

GTY_CLK_0C

MGTREFCLK0_128

LVDS

U33

U34

Table 8 : QSFP28 Reference Clocks

The QSFP28 cages are also located such that they can be clocked from a Si5328 jitter attenuator clock

multiplier. If jitter attenuation is required please see the reference documentation for the Si5328. https://

www.silabs.com/Support%20Documents/TechnicalDocs/Si5328.pdf

The Si5328 is configured with a 114.285MHz oscilator on XA and XB, SDA is at FPGA pin L29 (1.8V), SCL is at

FPGA pin L30 (1.8V) with external pull-ups included.

The Si5328 input clock comes from FPGA pins M29 and M30, and includes 100 Ohm AC coupled termination on

the 1.8V FPGA bank.

Signal

Target FPGA Input

I/O Standard

"P" pin

"N" pin

SI5328_REFCLK_OUT0

MGTREFCLK1_129

LVDS

L33

L34

SI5328_REFCLK_OUT1

MGTREFCLK1_128

LVDS

R33

R34

Table 9 : QSFP28 Jitter Attenuated Reference Clocks

3.2.5 FireFly

The two FireFly sites are located in MGT tile 125 and 126 and use a 161.1328125MHz default reference clock.

Note that this clock frequency can be changed to any arbitrary clock frequency up to 400MHz by re-programing

the Si5338 reprogrammable clock oscillator via system monitor. This can be done using the Alpha Data API or

over USB with the appropriate Alpha Data Software tools.

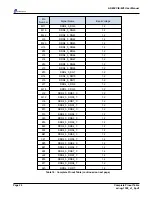

Signal

Target FPGA Input

I/O Standard

"P" pin

"N" pin

GTY_CLK_1B

MGTREFCLK0_126

LVDS

AE33

AE34

GTY_CLK_1C

MGTREFCLK0_125

LVDS

AJ33

AJ34

Table 10 : FireFly Reference Clocks

3.2.6 DDR4 SDRAM Reference Clocks

The two banks of DDR4 SDRAM memory each require a separate reference clock, as per Xilinx UltraScale MIG

design guidelines. The reference clocks for these interfaces are detailed below:

Both clocks are 300MHz by default.

Page 9

Functional Description

ad-ug-1308_v1_9.pdf