ADM-PCIE-9V5 User Manual

3.4 QSFP-DD

Four QSFP-DD cages are available at the front panel. These cages are capable of housing either QSFP28 or

QSFP-DD cables (backwards compatible). Both active optical and passive copper QSFP-DD/QSFP28

compatible models are fully compliant. The communication interface can run at up to 28Gbps per channel. Each

QSFP-DD cage has 8 channels (total maximum bandwidth of 224Gbps per cage). This cage is ideally suited for

8x 10G/25G, 2x 100G Ethernet, or any other protocol supported by the Xilinx GTY Transceivers. Please see

Xilinx User Guide UG578 for more details on the capabilities of the transceivers.

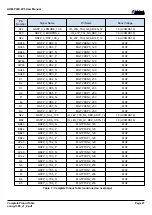

All QSFP-DD cages have control signals connected to the FPGA. Their connectivity is detailed in the

at the end of this document. The notation used in the pin assignments is QSFP_0*, QSFP_1*,

QSFP_2*, and QSFP_3*, with locations clarified in the diagram below.

The Management Interface of each QSFP-DD cage is connected to the FPGA, as detailed in

. The available signals are SDA/SCL (I2C), INT_L (interrupt), LPMODE (low power mode), RST_L (reset),

and MODPRS_L (module present).

Note:

The LPMODE (Low Power Mode) to the cage is pulled up by default. The FPGA can either (a) drive the

relevant LPMODE pin low or (b) issue I2C transactions in order to power-up a given QSFP-DD/QSFP28

module

Figure 12 : QSFP-DD Location

It is possible for Alpha Data to pre-fit the ADM-PCIE-9V5 with QSFP-DD and QSFP28 components. Please

contact sales@alpha-data.com for full details and options.

Alpha Data has tested the ADM-PCIE-9V5 with an array of passive cables from multiple manufacturers. Please

contact sales@alpha-data.com for more details on appropriate and available cables. Cable types include:

QSFP-DD to 8x SFP, QSFP-DD to 2x QSFP, and QSFP-DD to QSFP-DD.

Page 14

Functional Description

ad-ug-1385_v1_0.pdf