ADM-PCIE-9V5 User Manual

the front panel. Contact sales@alpha-data.com for front panel connector options.

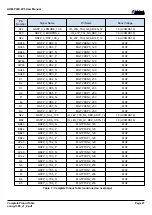

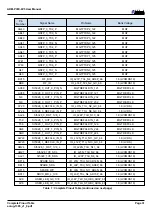

For pin locations, see signal name ISO_CLK in

.

The signal is isolated through a optical isolator part number TLP2367 with 220 ohm of series resistance.

Page 21

Functional Description

ad-ug-1385_v1_0.pdf