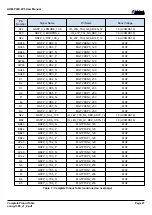

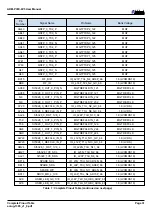

ADM-PCIE-9V5 User Manual

Pin

Number

Signal Name

Pin Name

Bank Voltage

P22

QSFP_0_LPMODE_1V8

IO_L5N_T0U_N9_AD14N_72

1.8 (LVCMOS18)

P20

QSFP_0_MODPRS_L

IO_L1P_T0L_N0_DBC_72

1.8 (LVCMOS18)

R22

QSFP_0_RST_1V8_L

IO_L5P_T0U_N8_AD14P_72

1.8 (LVCMOS18)

BC46

QSFP_0_RX0_N

MGTYRXN0_120

MGT

BC45

QSFP_0_RX0_P

MGTYRXP0_120

MGT

BA46

QSFP_0_RX1_N

MGTYRXN1_120

MGT

BA45

QSFP_0_RX1_P

MGTYRXP1_120

MGT

AW46

QSFP_0_RX2_N

MGTYRXN2_120

MGT

AW45

QSFP_0_RX2_P

MGTYRXP2_120

MGT

AU46

QSFP_0_RX3_N

MGTYRXN3_120

MGT

AU45

QSFP_0_RX3_P

MGTYRXP3_120

MGT

K1

QSFP_0_RX4_N

MGTYRXN0_233

MGT

K2

QSFP_0_RX4_P

MGTYRXP0_233

MGT

H1

QSFP_0_RX5_N

MGTYRXN1_233

MGT

H2

QSFP_0_RX5_P

MGTYRXP1_233

MGT

F1

QSFP_0_RX6_N

MGTYRXN2_233

MGT

F2

QSFP_0_RX6_P

MGTYRXP2_233

MGT

D1

QSFP_0_RX7_N

MGTYRXN3_233

MGT

D2

QSFP_0_RX7_P

MGTYRXP3_233

MGT

N22

QSFP_0_SCL_1V8

IO_L4P_T0U_N6_DBC_AD7P_72

1.8 (LVCMOS18)

M22

QSFP_0_SDA_1V8

IO_L4N_T0U_N7_DBC_AD7N_72

1.8 (LVCMOS18)

BD43

QSFP_0_TX0_N

MGTYTXN0_120

MGT

BD42

QSFP_0_TX0_P

MGTYTXP0_120

MGT

BB43

QSFP_0_TX1_N

MGTYTXN1_120

MGT

BB42

QSFP_0_TX1_P

MGTYTXP1_120

MGT

AY43

QSFP_0_TX2_N

MGTYTXN2_120

MGT

AY42

QSFP_0_TX2_P

MGTYTXP2_120

MGT

AV43

QSFP_0_TX3_N

MGTYTXN3_120

MGT

AV42

QSFP_0_TX3_P

MGTYTXP3_120

MGT

G4

QSFP_0_TX4_N

MGTYTXN0_233

MGT

G5

QSFP_0_TX4_P

MGTYTXP0_233

MGT

F6

QSFP_0_TX5_N

MGTYTXN1_233

MGT

F7

QSFP_0_TX5_P

MGTYTXP1_233

MGT

E4

QSFP_0_TX6_N

MGTYTXN2_233

MGT

E5

QSFP_0_TX6_P

MGTYTXP2_233

MGT

Table 7 : Complete Pinout Table (continued on next page)

Page 27

Complete Pinout Table

ad-ug-1385_v1_0.pdf