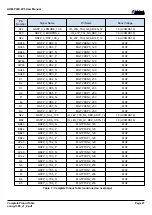

ADM-PCIE-9V5 User Manual

Pin

Number

Signal Name

Pin Name

Bank Voltage

AG40

QSFP_3_TX2_P

MGTYTXP2_122

MGT

AE41

QSFP_3_TX3_N

MGTYTXN3_122

MGT

AE40

QSFP_3_TX3_P

MGTYTXP3_122

MGT

AC41

QSFP_3_TX4_N

MGTYTXN0_125

MGT

AC40

QSFP_3_TX4_P

MGTYTXP0_125

MGT

AA41

QSFP_3_TX5_N

MGTYTXN1_125

MGT

AA40

QSFP_3_TX5_P

MGTYTXP1_125

MGT

W41

QSFP_3_TX6_N

MGTYTXN2_125

MGT

W40

QSFP_3_TX6_P

MGTYTXP2_125

MGT

U41

QSFP_3_TX7_N

MGTYTXN3_125

MGT

U40

QSFP_3_TX7_P

MGTYTXP3_125

MGT

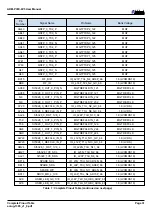

BC15

RF_DIR

IO_L21P_T3L_N4_AD8P_66

1.8 (LVCMOS18)

BB9

RF_IO

IO_L14P_T2L_N2_GC_66

1.8 (LVCMOS18)

AH39

SI5328_0_OUT_0_PIN_N

MGTREFCLK1N_121

MGT REFCLK

AH38

SI5328_0_OUT_0_PIN_P

MGTREFCLK1P_121

MGT REFCLK

N8

SI5328_0_OUT_1_PIN_N

MGTREFCLK1N_232

MGT REFCLK

N9

SI5328_0_OUT_1_PIN_P

MGTREFCLK1P_232

MGT REFCLK

AY23

SI5328_0_REFCLK_IN_N

IO_L11N_T1U_N9_GC_64

1.8 (LVDS)

AY24

SI5328_0_REFCLK_IN_P

IO_L11P_T1U_N8_GC_64

1.8 (LVDS)

AL24

SI5328_0_RST_1V8_L

IO_L24P_T3U_N10_64

1.8 (LVCMOS18)

T39

SI5328_1_OUT_0_PIN_N

MGTREFCLK1N_126

MGT REFCLK

T38

SI5328_1_OUT_0_PIN_P

MGTREFCLK1P_126

MGT REFCLK

AN8

SI5328_1_OUT_1_PIN_N

MGTREFCLK1N_224

MGT REFCLK

AN9

SI5328_1_OUT_1_PIN_P

MGTREFCLK1P_224

MGT REFCLK

AW22

SI5328_1_REFCLK_IN_N

IO_L12N_T1U_N11_GC_64

1.8 (LVDS)

AW23

SI5328_1_REFCLK_IN_P

IO_L12P_T1U_N10_GC_64

1.8 (LVDS)

AM24

SI5328_1_RST_1V8_L

IO_L24N_T3U_N11_64

1.8 (LVCMOS18)

AM21

SI5328_1V8_SCL

IO_L23N_T3U_N9_64

1.8 (LVCMOS18)

AL21

SI5328_1V8_SDA

IO_L23P_T3U_N8_64

1.8 (LVCMOS18)

BF14

SPARE_SCL

IO_L5N_T0U_N9_AD14N_66

1.8 (LVCMOS18)

BE15

SPARE_SDA

IO_L6P_T0U_N10_AD6P_66

1.8 (LVCMOS18)

BF15

SPARE_WP

IO_L6N_T0U_N11_AD6N_66

1.8 (LVCMOS18)

BC11

SRVC_MD_L_1V8

IO_L3P_T0L_N4_AD15P_66

1.8 (LVCMOS18)

AV9

USER_LED_G0_1V8

IO_L16P_T2U_N6_QBC_AD3P_66

1.8 (LVCMOS18)

AV8

USER_LED_G1_1V8

IO_L16N_T2U_N7_QBC_AD3N_66

1.8 (LVCMOS18)

Table 7 : Complete Pinout Table (continued on next page)

Page 31

Complete Pinout Table

ad-ug-1385_v1_0.pdf