ADM-SDEV-BASE/XCKU060 User Manual

V1.0 - 27th November 2018

1 Introduction

The ADM-SDEV-BASE/XCKU060 shall be the base board at the core of the ADA-SDEV-KIT1 space FPGA

development kit, enabling customers interested in space grade FPGAs to prototype their applications on a

compatible XCKU060-1I device.

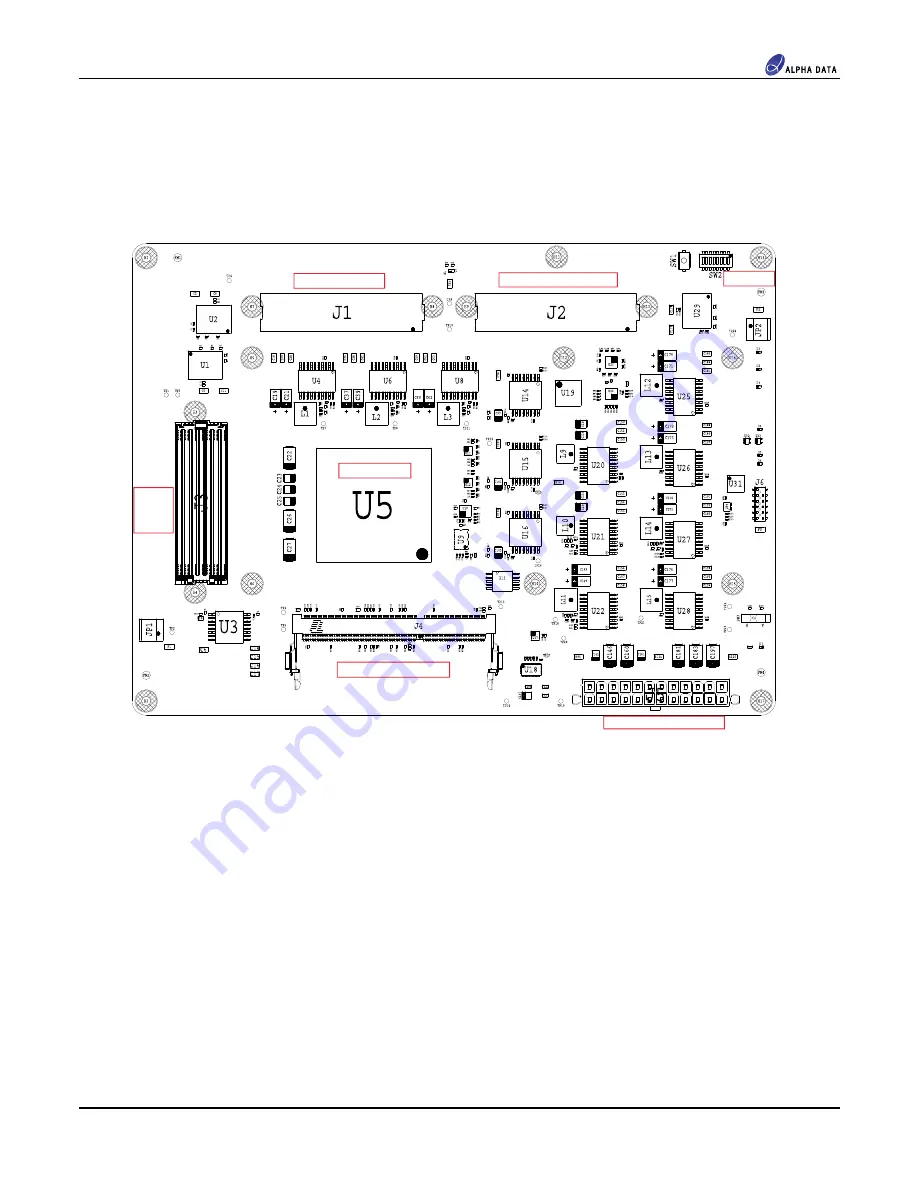

LPC FMC Socket

CONFIG FMC Socket

KU060 FPGA

HPC

FMC+

Socket

DDR3 SODIMM Socket

ATX Power Connector

Switches

Figure 1 : ADM-SDEV-BASE/XCKU060 Top View

Page 1

Introduction

ad-ug-1360_v1_0.pdf