ADM-VPX3-9Z2 User Manual

V1.1 - 16th January 2020

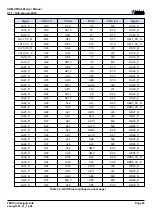

3.5.1 IO Delay Reference Clock (FABRIC_CLK)

The fixed reference clock FABRIC_CLK is a differential LVDS signal.

FABRIC_CLK is used as the reference clock for the IO delay control block (IDELAYCTRL).

Signal

Frequency

Target FPGA Input

IO Standard

"P" pin

"N" pin

FABRIC_CLK

300 MHz

IO BANK 47

LVDS

G21

F21

Table 9 : DDR REFCLK Connections

3.5.2 Fixed 100MHz Reference clock REFCLK100M

A fixed 100MHz reference clock is available on the board.

Signal

Frequency

Target FPGA Input

IO

Standard

"P" pin

REFCLK100M[0]

100 MHz

PS_505_MGTREFCLK_0 LVDS

AA27

REFCLK100M[1]

100 MHz

IO BANK 48

LVDS

E17

REFCLK100M[2]

100 MHz

MGTREFCLK1_230

LVDS

B10

REFCLK100M[3]

100 MHz

MGTREFCLK1_128

LVDS

N27

Table 10 : REFCLK100M Connections

3.5.3 Programmable Clocks (PROGCLK1 and PROGCLK2)

There are two programable clock sources that are forwarded throughout the FPGA. These clocks can be

programmed via the avr2util utility contained within the Alpha Data ADM-VPX3-9Z2 SDK. PROGCLK1 and

PROGCLK2 are generated by a dedicated programmable clock generator IC and offer extremely high frequency

resolutions (1ppm increments).

Signal

Frequency

Target FPGA Input

IO Standard

"P" pin

"N" pin

PROGCLK1[0]

5 - 400 MHz

PS_505_MGTREFCLK_1 LVDS

W27

W28

PROGCLK1[1]

5 - 400 MHz

IO BANK 67

LVDS

R10

R9

PROGCLK1[2]

5 - 400 MHz

MGTREFCLK1_228

LVDS

J8

J7

PROGCLK1[3]

5 - 400 MHz

MGTREFCLK1_129

LVDS

J27

J28

Table 11 : PROGCLK1 Connections

Note: PROGCLK1[3:0] are all buffered copies of the same clock signal.

Signal

Frequency

Target FPGA Input

IO Standard

"P" pin

"N" pin

PROGCLK2[0]

5 - 400 MHz

IO BANK 48

LVDS

E19

D19

PROGCLK2[1]

5 - 400 MHz

IO BANK 64

LVDS

AK8

AK7

PROGCLK2[2]

5 - 400 MHz

MGTREFCLK1_130

LVDS

E27

E28

PROGCLK2[3]

5 - 400 MHz

MGTREFCLK1_229

LVDS

E8

E7

Table 12 : PROGCLK2 Connections

Note: PROGCLK2[3:0] are all buffered copies of the same clock signal.

Page 12

Functional Description

ad-ug-1323_v1_1.pdf