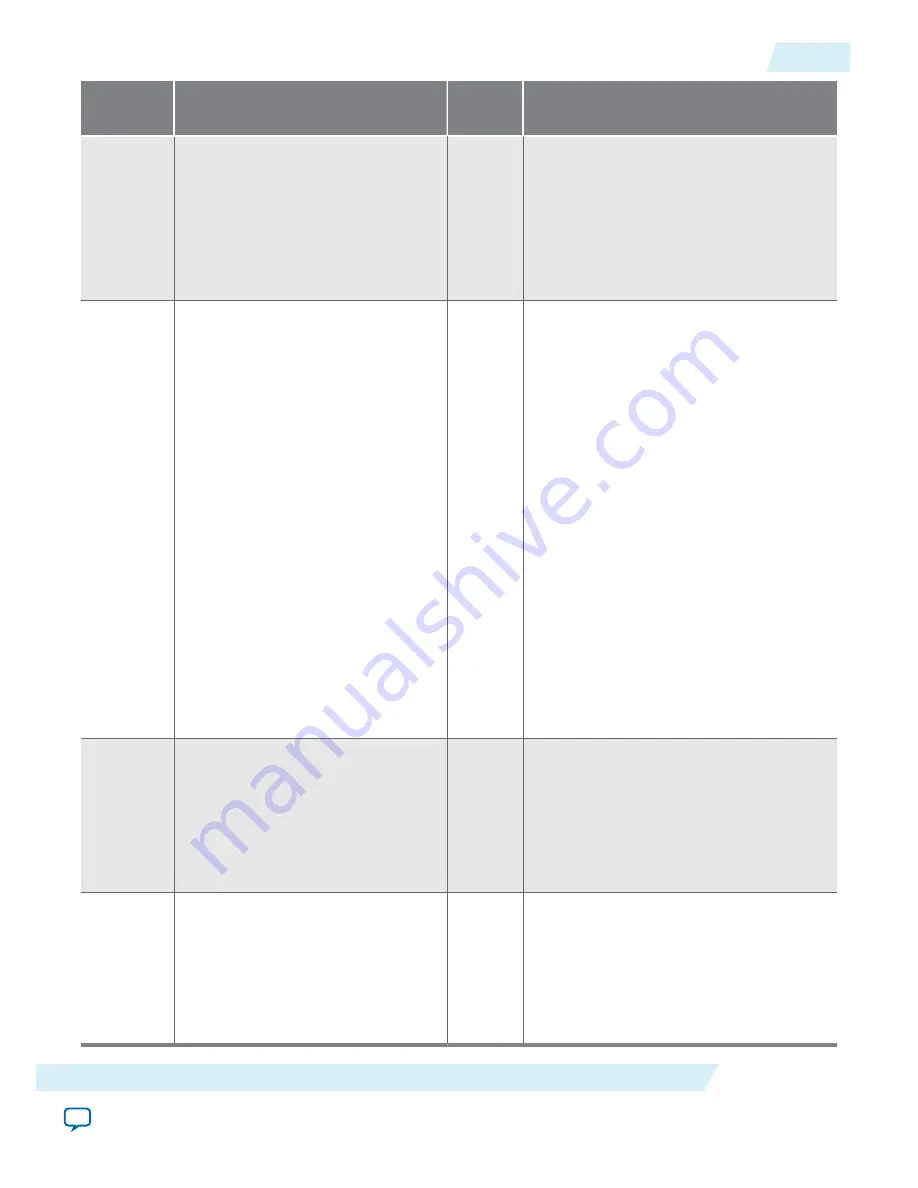

Address

Offset

Register

Access

Description

0x010C

EP Write Status and Descriptor

FIFO Base (High)

RW

Specifies the upper 32 bits of the base

address of the write descriptor table in

Endpoint memory. The read DMA fetches

the table from Root Complex memory and

writes the table to this location. Software

must program this register before

programming the lower 32-bit register at

offset 0x108.

0x0110

WR_DMA_LAST_PTR

RW

When read, returns the ID of the last

descriptor requested. If no DMA request

is outstanding or the DMA is in reset,

returns a value 0xFF.

When written, specifies the ID of the last

descriptor requested. The difference

between the value read and the value

written is the number of descriptors to be

processed.

For example, if the value reads 4, the last

descriptor requested is 4. To specify 5

more descriptors, software should write a

9 into the

RD_DMA_LAST_PTR

register. The

DMA executes 5 more descriptors.

The

Descriptor ID

loops back to 0 after

reaching

WR_TABLE_SIZE

.

For example, if the

WR_TABLE_SIZE

value

read is 126 and you want to execute three

more descriptors, software must write 127,

and then 1 into the

WR_DMA_LAST_PTR

register.

0x0114

WR_TABLE_SIZE

RW

Specifies the size of the Read descriptor

table. Set to the number of descriptors - 1.

By default,

WR_TABLE_SIZE

is set to 127.

This value specifies the last

Descriptor

ID

. To change the

RC Write Status and

Descriptor Base (Low)

base address, all

descriptors specified by the

WR_TABLE_

SIZE

must be exhausted.

0x0118

WR_CONTROL

RW

[31:1] Reserved.

[0]

Done

. When set, the Descriptor

Controller writes the

Done

bit for each

descriptor in the status table. The

Descriptor Controller sends a single MSI

interrupt after the final descriptor

completes.

UG-01145_avmm_dma

2015.11.02

DMA Descriptor Controller Registers

7-21

Registers

Altera Corporation

Send Feedback