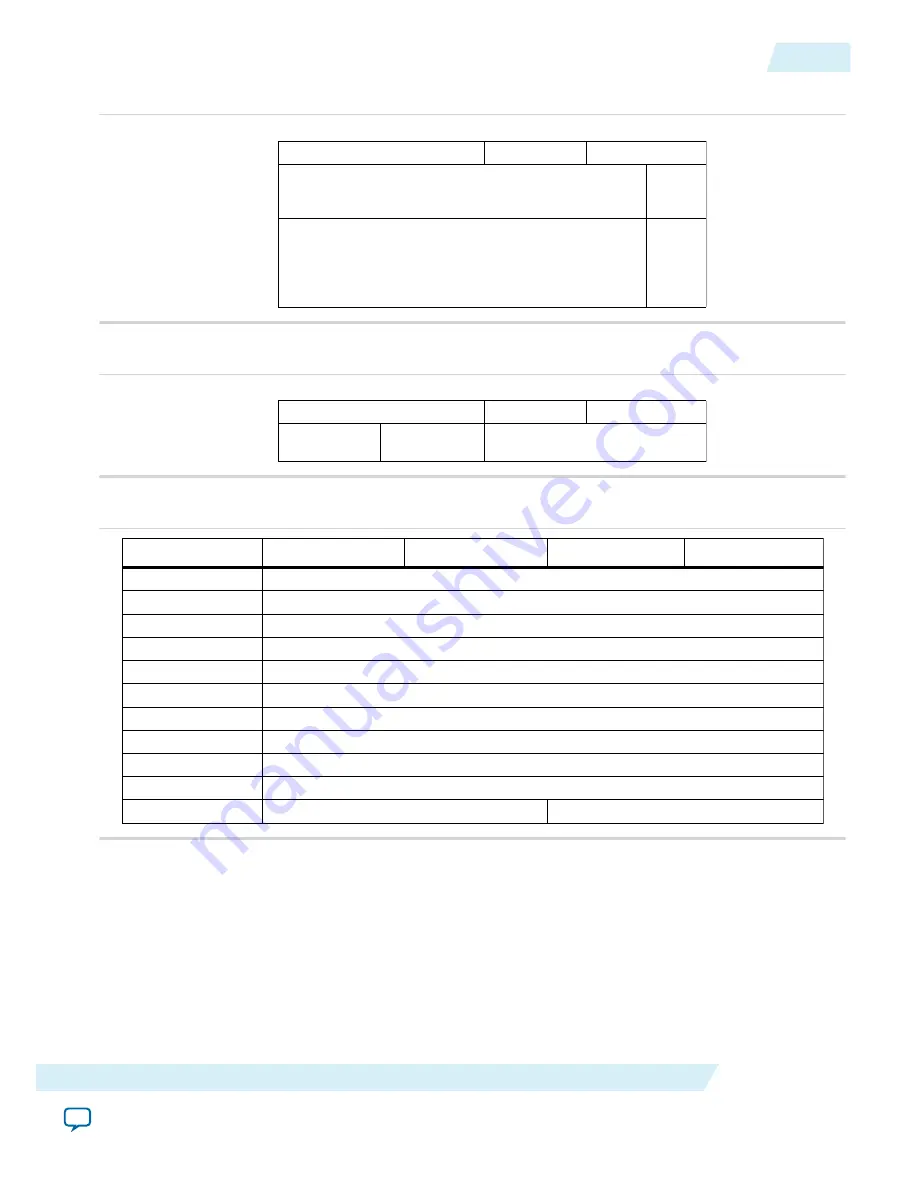

Figure 7-4: MSI-X Capability Structure

0x068

0x06C

0x070

Message Control

Next Cap Ptr

MSI-X Table Offset

MSI-X Pending Bit Array (PBA) Offset

31

24 23

16 15

8 7

0

Capability ID

3 2

MSI-X

Table BAR

Indicator

MSI-X

Pending

Bit Array

- BAR

Indicator

Figure 7-5: Power Management Capability Structure - Byte Address Offsets and Layout

0x078

0x07C

Capabilities Register

Next Cap Ptr

Data

31

24 23

16 15

8 7

0

Capability ID

Power Management Status and Control

PM Control/Status

Bridge Extensions

Figure 7-6: PCI Express AER Extended Capability Structure

Byte Offset

31:24

23:16

15:8

7:0

0x800

0x804

Uncorrectable Error Status Register

PCI Express Enhanced Capability Register

Uncorrectable Error Severity Register

Uncorrectable Error Mask Register

0x808

0x80C

0x810

0x814

0x818

0x81C

0x82C

0x830

0x834

Correctable Error Status Register

Correctable Error Mask Register

Advanced Error Capabilities and Control Register

Header Log Register

Root Error Command Register

Root Error Status Register

Error Source Identification Register

Correctable Error Source Identification Register

Figure 7-7: PCI Express Capability Structure - Byte Address Offsets and Layout

In the following table showing the PCI Express Capability Structure, registers that are not applicable to a

device are reserved.

Note: The Avalon-MM with DMA interface does not support Root Ports.

UG-01145_avmm_dma

2015.11.02

PCI Express Capability Structures

7-7

Registers

Altera Corporation

Send Feedback