The Avalon-MM with DMA Arria 10 variants include an Avalon-MM DMA bridge implemented in soft

logic that operates as a front end to the hardened protocol stack. The following table shows the typical

expected device resource utilization for selected configurations using the current version of the Quartus

Prime software targeting an Arria 10 device. With the exception of M20K memory blocks, the numbers of

ALMs and logic registers are rounded up to the nearest 50.

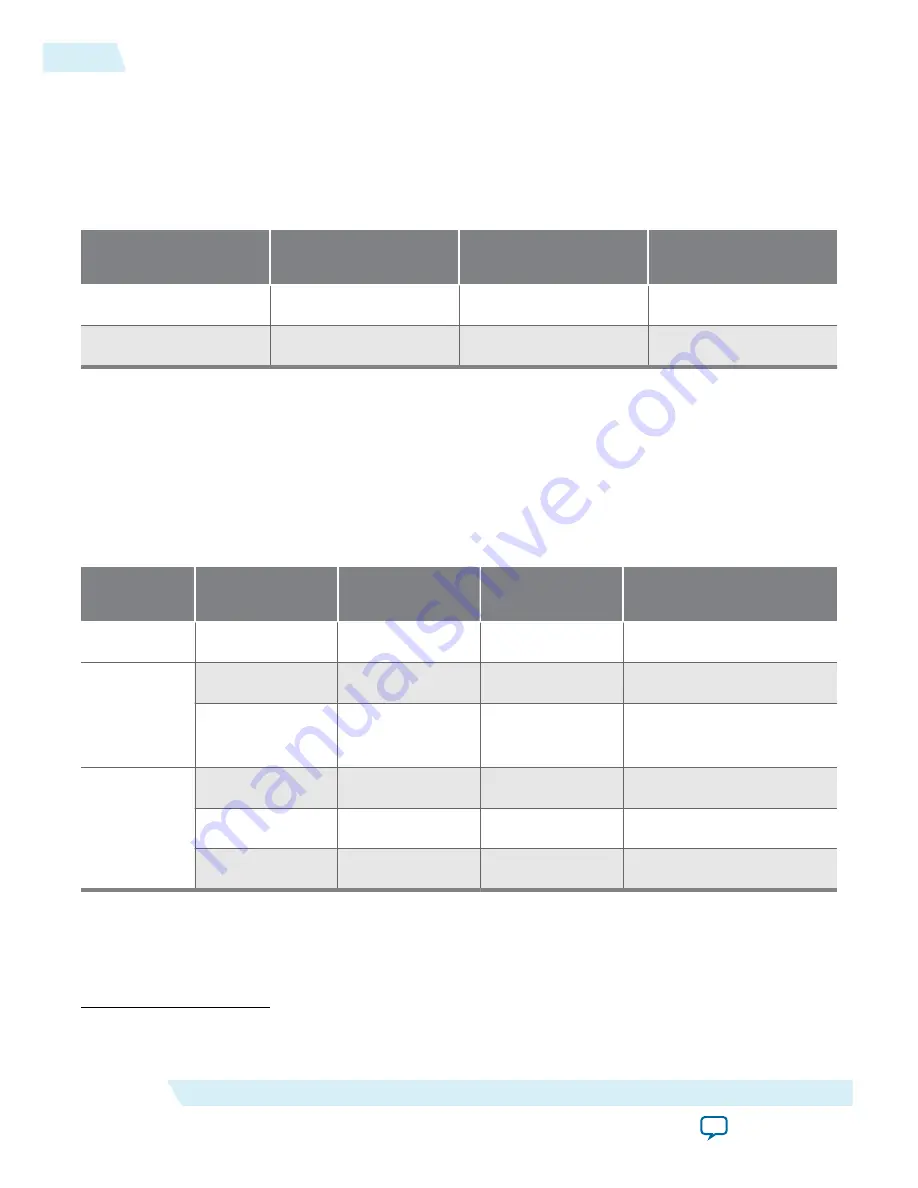

Table 1-6: Performance and Resource Utilization Arria 10 Avalon-MM DMA for PCI Express

Data Rate, Number of

Lanes, and Interface Width

ALMs

M20K Memory Blocks

Logic Registers

Gen2 x8 128

12700

19

22300

Gen3 x8 256

18000

47

31450

Related Information

Fitter Resources Reports

Recommended Speed Grades

Recommended speed grades are pending characterization of production Arria 10 devices.

Table 1-7: Arria 10 Recommended Speed Grades for All Avalon-MM Widths and Frequencies

Lane Rate

Link Width

Interface Width

Application Clock

Frequency (MHz)

Recommended Speed Grades

Gen1

×8

128 Bits

125

–1, –2, –3, –4

Gen2

×4

128 bits

125

–1, –2, –3, –4

×8

128 bits

250

–1, –2, –3

(1)

Gen3

×2

128 bits

125

–1, –2, –3

(1)

×4

128 bits

250

–1, –2, –3

(1)

×8

256 bits

250

–1, –2, –3

(1)

Related Information

•

Altera Software Installation and Licensing Manual

•

Setting up and Running Analysis and Synthesis

(1)

The -4 speed grade is also possible for this configuration; however, it requires significant effort by the end

user to close timing.

1-8

Recommended Speed Grades

UG-01145_avmm_dma

2015.11.02

Altera Corporation

Datasheet

Send Feedback