2–22

Chapter 2: Board Components

Memory

Cyclone IV GX Transceiver Starter Board Reference Manual

© March 2010 Altera

Corporation

Transceiver SMA Connectors (Optional)

Board references J9 and J8 are two optional input SMAs to the high-speed positive

and negative differential receiver channel while J11 and J10 are two optional output

SMAs from the high-speed positive and negative differential transmitter channel. By

default, the

GXB_RX1

channel of the FPGA is connected to the Ethernet PHY through

capacitor multiplexer C59 and C58, while the

GXB_TX1

channel is connected to the

Ethernet PHY through resistor multiplexer R53 and R52. You need to perform a solder

modification on the board if you intend to use the optional transceiver SMA

connectors. You can use these SMAs to connect to external circuit boards or

daughtercards for transceiver applications.

Table 2–27

shows the capacitor and resistor multiplexer locations to enable either the

default Ethernet PHY connection or the optional transceiver SMA connectors. The

capacitors multiplexer are 0.1-

μ

F capacitors and the multiplexer resistors are 0-

Ω

resistors.

Memory

This section describes the board's memory interface support and also their signal

names, types, and connectivity relative to the Cyclone IV GX device. The board has

the following memory interfaces:

■

SSRAM

■

Flash

SSRAM

The SSRAM device consists of a single standard synchronous SRAM, providing

18-Mb of memory with a 16-bit data bus. This device is part of the shared FSML bus

which connects to the flash memory, SRAM, and MAX

II CPLD EPM2210 System

Controller.

Table 2–28

lists the SSRAM

pin assignments, signal names, and functions. The signal

names and types are relative to the Cyclone IV GX device in terms of I/O setting and

direction.

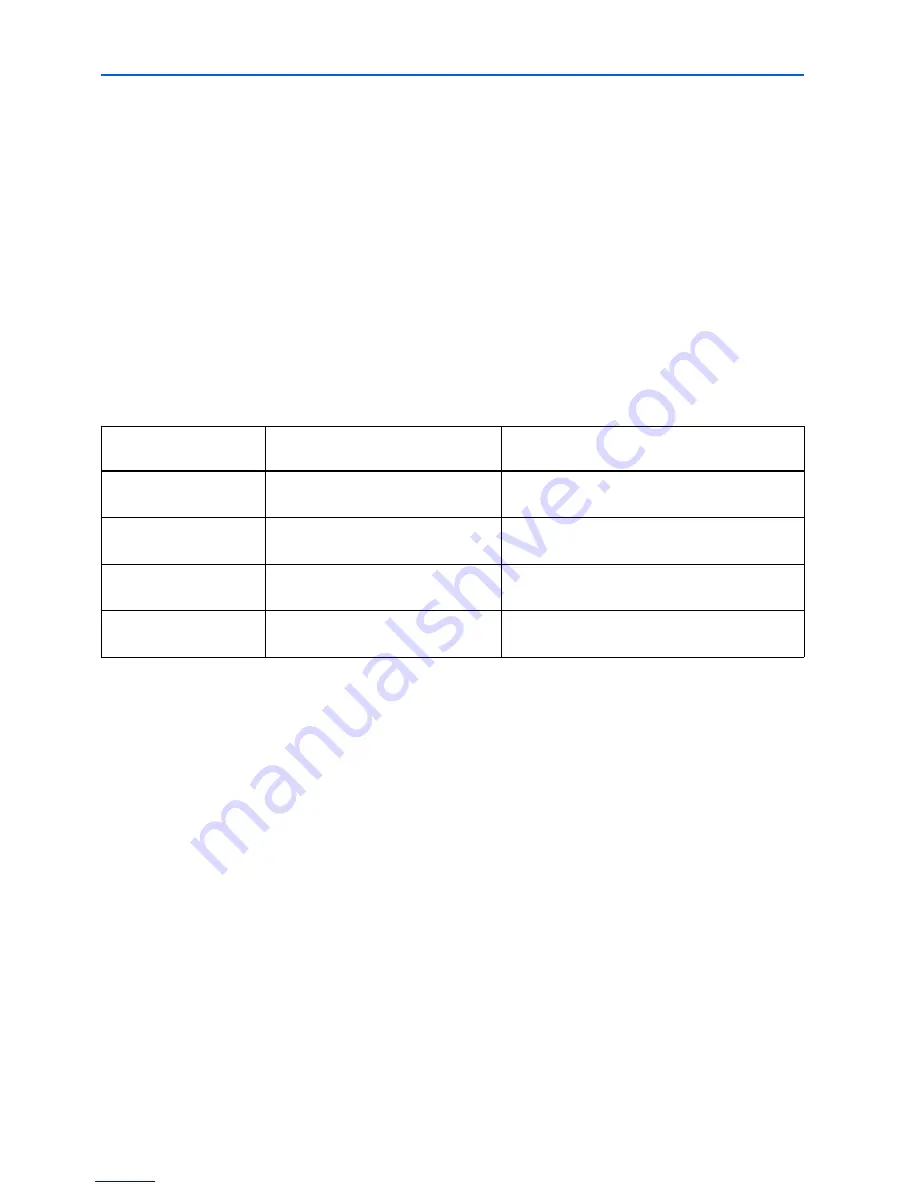

Table 2–27.

Multiplexer Locations for the Ethernet PHY Connection and Transceiver SMAs Connectors

Board Reference

Description

Multiplexer Location

C59, C58, C60, C57

Ethernet PHY RX enable

■

Populate C59 and C58

■

Unpopulate C60 and C57 (default)

R53, R52, R54, R51

Ethernet PHY TX enable

■

Populate R53 and R52

■

Unpopulate R54 and R51 (default)

C59, C58, C60, C57

Transceiver SMA RX enable

■

Populate C60 and C57

■

Unpopulate C59 and C58

R53, R52, R54, R51

Transceiver SMA TX enable

■

Populate R54 and R51

■

Unpopulate R53 and R52

electronic components distributor