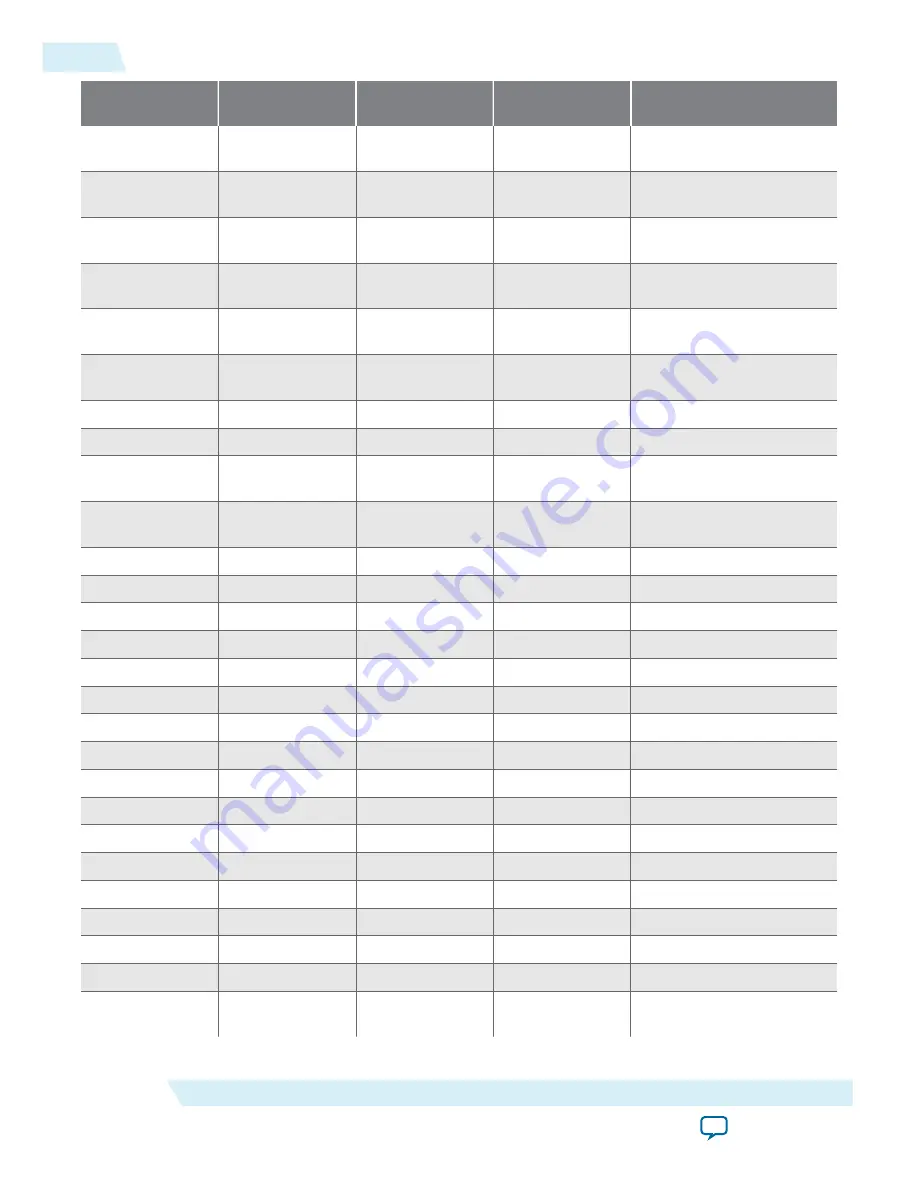

Board Reference

(U2)

Schematic Signal

Name

MAX 10 FPGA Pin

Number

I/O Standard

Description

U2.M1

LPDDR2_CA4

H22

1.2V HSUL

Command/Address Bus

Input

U2.G2

LPDDR2_CA5

D22

1.2V HSUL

Command/Address Bus

Input

U2.F2

LPDDR2_CA6

C22

1.2V HSUL

Command/Address Bus

Input

U2.F3

LPDDR2_CA7

E22

1.2V HSUL

Command/Address Bus

Input

U2.E3

LPDDR2_CA8

A21

1.2V HSUL

Command/Address Bus

Input

U2.E2

LPDDR2_CA9

B22

1.2V HSUL

Command/Address Bus

Input

U2.K1

LPDDR2_CKE

E21

1.2V HSUL

Clock Enable

U2.L1

LPDDR2_CSn

G22

1.2V HSUL

Chip Select

U2.J3

LPDDR2_CK

D18

Differential 1.2V

HSUL

Differential Input Clock

U2.H3

LPDDR2_CKn

E18

Differential 1.2V

HSUL

Differential Input Clock

U2.N8

LPDDR2_DQ0

N18

1.2V HSUL

Data Bus Byte Lane 0

U2.M8

LPDDR2_DQ1

N20

1.2V HSUL

Data Bus Byte Lane 0

U2.M7

LPDDR2_DQ2

M20

1.2V HSUL

Data Bus Byte Lane 0

U2.M9

LPDDR2_DQ3

M14

1.2V HSUL

Data Bus Byte Lane 0

U2.M6

LPDDR2_DQ4

M18

1.2V HSUL

Data Bus Byte Lane 0

U2.L7

LPDDR2_DQ5

M15

1.2V HSUL

Data Bus Byte Lane 0

U2.L8

LPDDR2_DQ6

L20

1.2V HSUL

Data Bus Byte Lane 0

U2.L9

LPDDR2_DQ7

L18

1.2V HSUL

Data Bus Byte Lane 0

U2.G9

LPDDR2_DQ8

K20

1.2V HSUL

Data Bus Byte Lane 1

U2.G8

LPDDR2_DQ9

K19

1.2V HSUL

Data Bus Byte Lane 1

U2.G7

LPDDR2_DQ10

K18

1.2V HSUL

Data Bus Byte Lane 1

U2.F6

LPDDR2_DQ11

H19

1.2V HSUL

Data Bus Byte Lane 1

U2.F9

LPDDR2_DQ12

H20

1.2V HSUL

Data Bus Byte Lane 1

U2.F7

LPDDR2_DQ13

H18

1.2V HSUL

Data Bus Byte Lane 1

U2.F8

LPDDR2_DQ14

J14

1.2V HSUL

Data Bus Byte Lane 1

U2.E8

LPDDR2_DQ15

J18

1.2V HSUL

Data Bus Byte Lane 1

U2.L6

LPDDR2_DQS0

L14

Differential 1.2V

HSUL

Data Strobe P Byte Lane 0

3-20

LPDDR2

UG-20006

2016.02.29

Altera Corporation

Board Components

Send Feedback