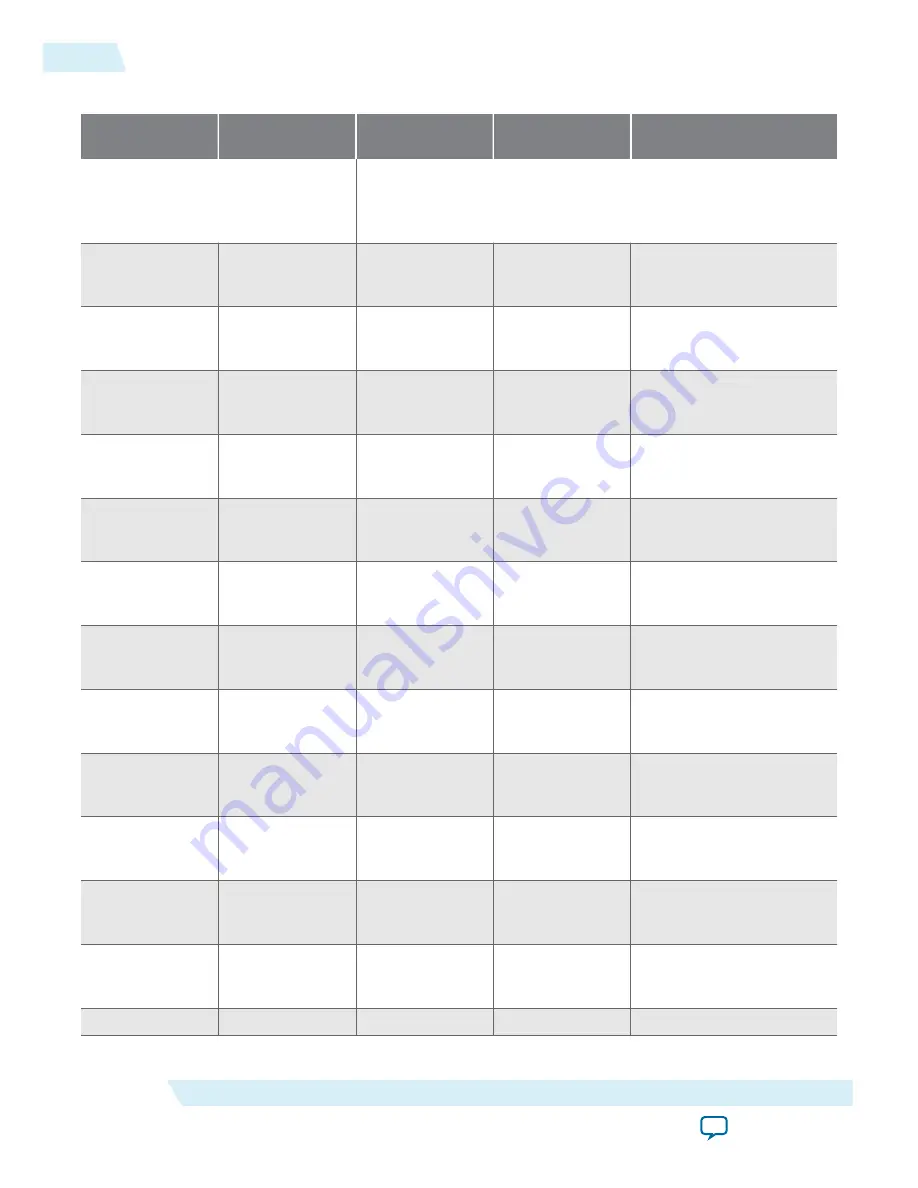

Table 3-21: MIPI CSI-2 Receiver (for OV5640 module) Pin Assignments, Signal Names and Functions

Source

Schematic Signal

Name

Device/Pin Number

I/O Standard

Description

J3

(Cable needed to interface OV5640

module)

Wurth Electronics 68711614522

J3.6

OV5640_CLK_

HS_P

MAX 10/V10

2.5V LVDS

Differential input clock

(high speed, positive

terminal)

J3.5

OV5640_CLK_

HS_N

MAX 10/V9

2.5V LVDS

Differential input clock

(high speed, negative

terminal)

J3.6

OV5640_CLK_

LP_P

MAX 10/R15

1.2V HSTL

Differential input clock

(low power, positive

terminal)

J3.5

OV5640_CLK_

LP_N

MAX 10/R14

1.2V HSTL

Differential input clock

(high speed, positive

terminal)

J3.9

OV5640_DATA_

HS_P1

MAX 10/AB13

2.5V LVDS

Differential input data

Lane1 (high

speed,positive terminal)

J3.8

OV5640_DATA_

HS_N1

MAX 10/AB12

2.5V LVDS

Differential input data

Lane1 (high

speed,negative terminal)

J3.9

OV5640_DATA_

LP_P1

MAX 10/W19

1.2V HSTL

Differential input data

Lane1 (low power,positive

terminal)

J3.8

OV5640_DATA_

LP_N1

MAX 10/W20

1.2V HSTL

Differential input data

Lane1 (low

power,negative terminal)

J3.2

OV5640_DATA_

HS_P2

MAX 10/AB11

2.5V LVDS

Differential input data

Lane2 (high

speed,positive terminal)

J3.1

OV5640_DATA_

HS_N2

MAX 10/AB10

2.5V LVDS

Differential input data

Lane2 (high

speed,negative terminal)

J3.2

OV5640_DATA_

LP_P2

MAX 10/P15

1.2V HSTL

Differential input data

Lane2 (low power,positive

terminal)

J3.1

OV5640_DATA_

LP_N2

MAX 10/P14

1.2V HSTL

Differential input data

Lane2 (low

power,negative terminal)

J3.13

OV5640_SDC

MAX 10/M3

3.3V LVCMOS

Control Bus Clock

3-28

MIPI CSI-2 Receiver

UG-20006

2016.02.29

Altera Corporation

Board Components

Send Feedback