Chapter 2: Board Components

2–11

MAX II CPLD EPM2210 System Controller

November 2010

Altera Corporation

Stratix IV GX FPGA Development Board, 530 Edition Reference Manual

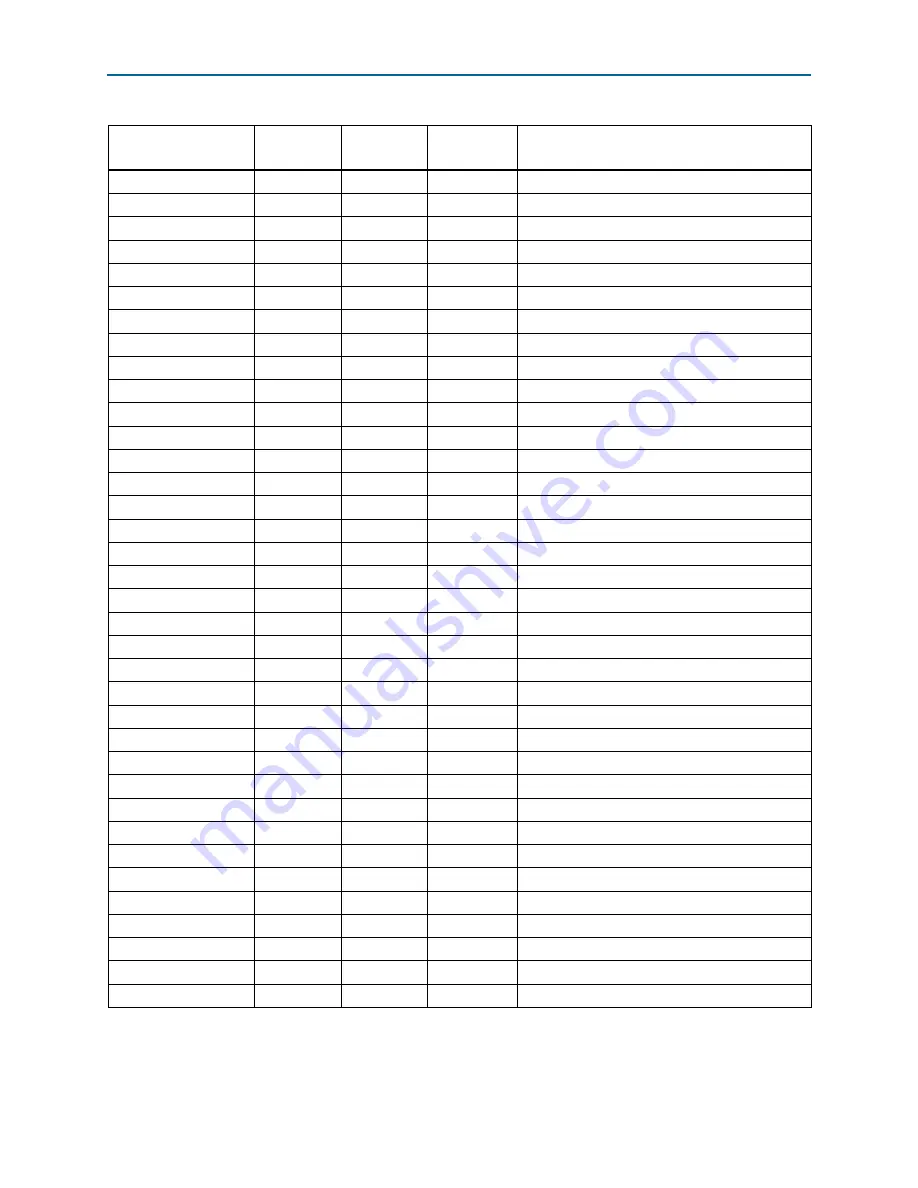

OVERTEMPn

2.5-V

P5

—

Temperature monitor over-temperature indicator

ALERTn

2.5-V

M2

—

Temperature monitor alert

PHASE_0

2.5-V

T6

—

Power clock 0 degrees

PHASE_90

2.5-V

R7

—

Power clock 90 degrees

PHASE_135

2.5-V

P8

—

Power clock 135 degrees

PHASE_270

2.5-V

T7

—

Power clock 270 degrees

MAX_ERROR

2.5-V

G3

—

FPGA configuration error LED

MAX_LOAD

2.5-V

G2

—

FPGA configuration active LED

MAX_CONF_DONEn

2.5-V

E15

—

FPGA configuration done LED

USB_LED

2.5-V

F12

—

Embedded USB-Blaster active

HSMA_PRSNTn

2.5-V

J16

—

HSMC port A present

HSMB_PRSNTn

2.5-V

J13

—

HSMC port B present

MAX_DIP

2.5-V

F15

—

DIP-reserved

USB_DISABLEn

2.5-V

G14

—

DIP-embedded USB-Blaster disable

LCD_PWRMON

2.5-V

R5

—

DIP-MAX2 LCD drive enable

FAN_FORCE_ON

2.5-V

P7

—

DIP-force fan on switch

CLK_SEL

2.5-V

T5

—

DIP-clock select SMA or oscillator

CLK_ENABLE

2.5-V

N7

—

DIP-clock oscillator enable

PGM3

2.5-V

J3

—

Rotary switch input

PGM2

2.5-V

K1

—

Rotary switch input

PGM1

2.5-V

J4

—

Rotary switch input

PGM0

2.5-V

J2

—

Rotary switch input

RESET_CONFIGn

2.5-V

K2

—

Force FPGA configuration push-button switch

CPU_RESETn

2.5-V

M9

V34

Reset push-button switch

SRAM_MODE

2.5-V

P4

—

SRAM mode

SRAM_ZZ

2.5-V

L14

—

SRAM sleep mode

CLK50_EN

2.5-V

G12

—

50 MHz oscillator enable

CLK100_EN

2.5-V

G16

—

100 MHz oscillator enable

CLK100_SDA

2.5-V

A2

—

100 MHz programming data

CLK100_SCL

2.5-V

C15

—

100 MHz programming clock

CLK125_EN

2.5-V

H16

—

125 MHz oscillator enable

CLK148_EN

2.5-V

H13

—

148 MHz oscillator enable

CLK155_EN

2.5-V

H15

—

155 MHz oscillator enable

CLK156_EN

2.5-V

H14

—

156 MHz oscillator enable

CLKIN_50

2.5-V

J5

AC34

50 MHz clock input

CLK_CONFIG

2.5-V

J12

—

125 MHz configuration clock

Table 2–6. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 4 of 4)

Schematic Signal

Name

I/O Standard

EPM2210

Pin Number

EP4SGX230

Pin Number

Description