Chapter 6: IP Core Interfaces

6–21

Avalon-ST TX Interface

June 2012

Altera Corporation

Stratix V Hard IP for PCI Express

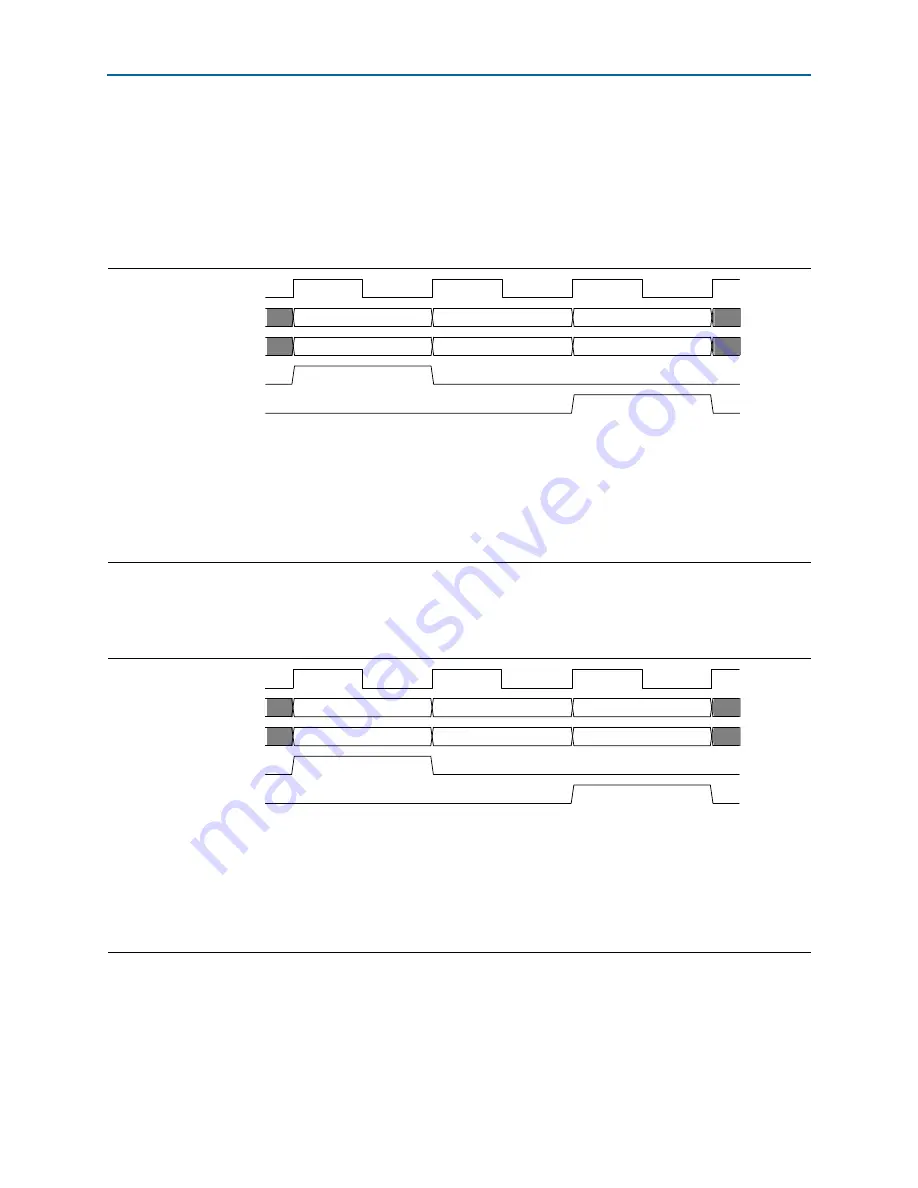

Data Alignment and Timing for the 64-Bit Avalon-ST TX Interface

illustrates the mapping between Avalon-ST TX packets and PCI Express

TLPs for three dword header TLPs with non-qword aligned addresses on a 64-bit bus.

(

Figure 6–2 on page 6–8

illustrates the storage of non-qword aligned data.)

Non-qword aligned address occur when

address[2]

is set. When address[2] is set,

tx_st_data[63:32]

contains

Data0

and

tx_st_data[31:0]

contains dword

header2

.

illustrates the mapping between Avalon-ST TX packets and PCI Express

TLPs for a four dword header with qword aligned addresses on a 64-bit bus.

Figure 6–19. 64-Bit Avalon-ST tx_st_data Cycle Definition for 3-Dword Header TLP with Non-Qword Aligned Address

Notes to

(1) Header0 ={pcie_hdr_byte0, pcie_hdr _byte1, pcie_hdr _byte2, pcie_hdr _byte3}

(2) Header1 = {pcie_hdr_byte4, pcie_hdr _byte5, header pcie_hdr byte6, pcie_hdr _byte7}

(3) Header2 = {pcie_hdr _byte8, pcie_hdr _byte9, pcie_hdr _byte10, pcie_hdr _byte11}

(4) Data0 = {pcie_data_byte3, pcie_data_byte2, pcie_data_byte1, pcie_data_byte0}

(5) Data1 = {pcie_data_byte7, pcie_data_byte6, pcie_data_byte5, pcie_data_byte4}

(6) Data2 = {pcie_data_byte11, pcie_data_byte10, pcie_data_byte9, pcie_data_byte8}

pld_clk

tx_st_data[63:32]

tx_st_data[31:0]

tx_st_sop

tx_st_eop

Header1

Data0

Data2

Header0

Header2

Data1

Figure 6–20. 64-Bit Avalon-ST tx_st_data Cycle Definition for 4-Dword TLP with Qword Aligned Address

Notes to

(1) Header0 = {pcie_hdr_byte0, pcie_hdr _byte1, pcie_hdr _byte2, pcie_hdr _byte3}

(2) Header1 = {pcie_hdr _byte4, pcie_hdr _byte5, pcie_hdr byte6, pcie_hdr _byte7}

(3) Header2 = {pcie_hdr _byte8, pcie_hdr _byte9, pcie_hdr _byte10, pcie_hdr _byte11}

(4) Header3 = pcie_hdr _byte12, pcie_hdr _byte13, header_byte14, pcie_hdr _byte15}, 4 dword header only

(5) Data0 = {pcie_data_byte3, pcie_data_byte2, pcie_data_byte1, pcie_data_byte0}

(6) Data1 = {pcie_data_byte7, pcie_data_byte6, pcie_data_byte5, pcie_data_byte4}

pld_clk

tx_st_data[63:32]

tx_st_data[31:0]

tx_st_sop

tx_st_eop

Header1

Header3

Data1

Header0

Header2

Data0