Chapter 6: IP Core Interfaces

6–55

Physical Layer Interface Signals

June 2012

Altera Corporation

Stratix V Hard IP for PCI Express

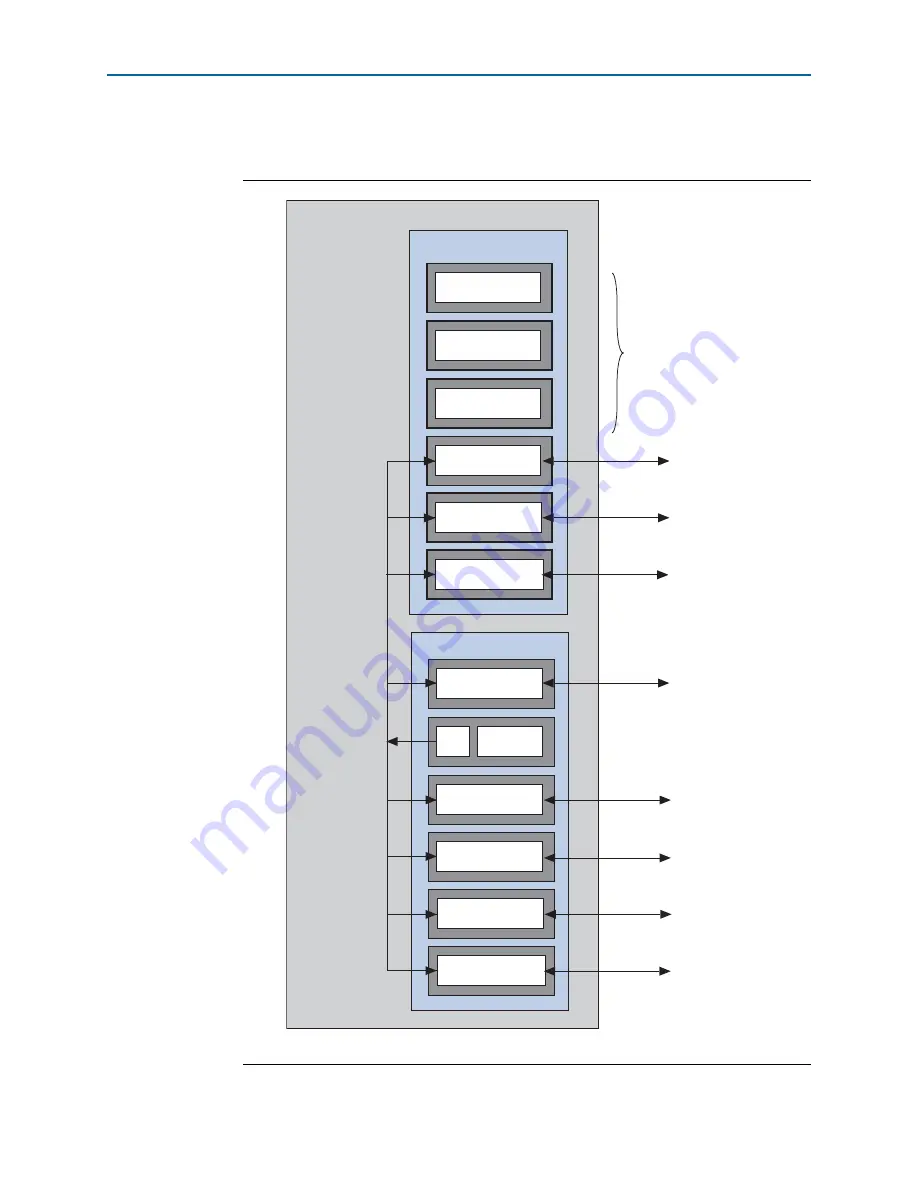

Figure 6–42

shows the channel placement for Gen1 and Gen2 ×8 variants when you

select the CMU PLL.

Figure 6–42. Channel Placement Gen1 and Gen2 ×8 Variants Using CMU PLL

Channel 0 -Data

Channel 1 - Data

Channel 2 - Data

Channel 4

- CMU PLL

Channel 5 - Data

Channel 3 - Data

T

r

ansceive

r

Bank 1

Gen1 and Gen2 x8

T

r

ansceive

r

Bank 0

Channel 6 - Data

Available

for Other

Protocols

Channel 7 - Data

Channel 8 - Data

Channel 10

Channel 11

PCS Clock and

Con

tr

ol Signals

Channel 9

CCD

CCD = Central Clock Divider

PCI Express Lane 0

PCI Express Lane 1

PCI Express Lane 2

PCI Express Lane 3

PCI Express Lane 4

Unavailable Channel

PCI Express Lane 5

PCI Express Lane 6

PCI Express Lane 7