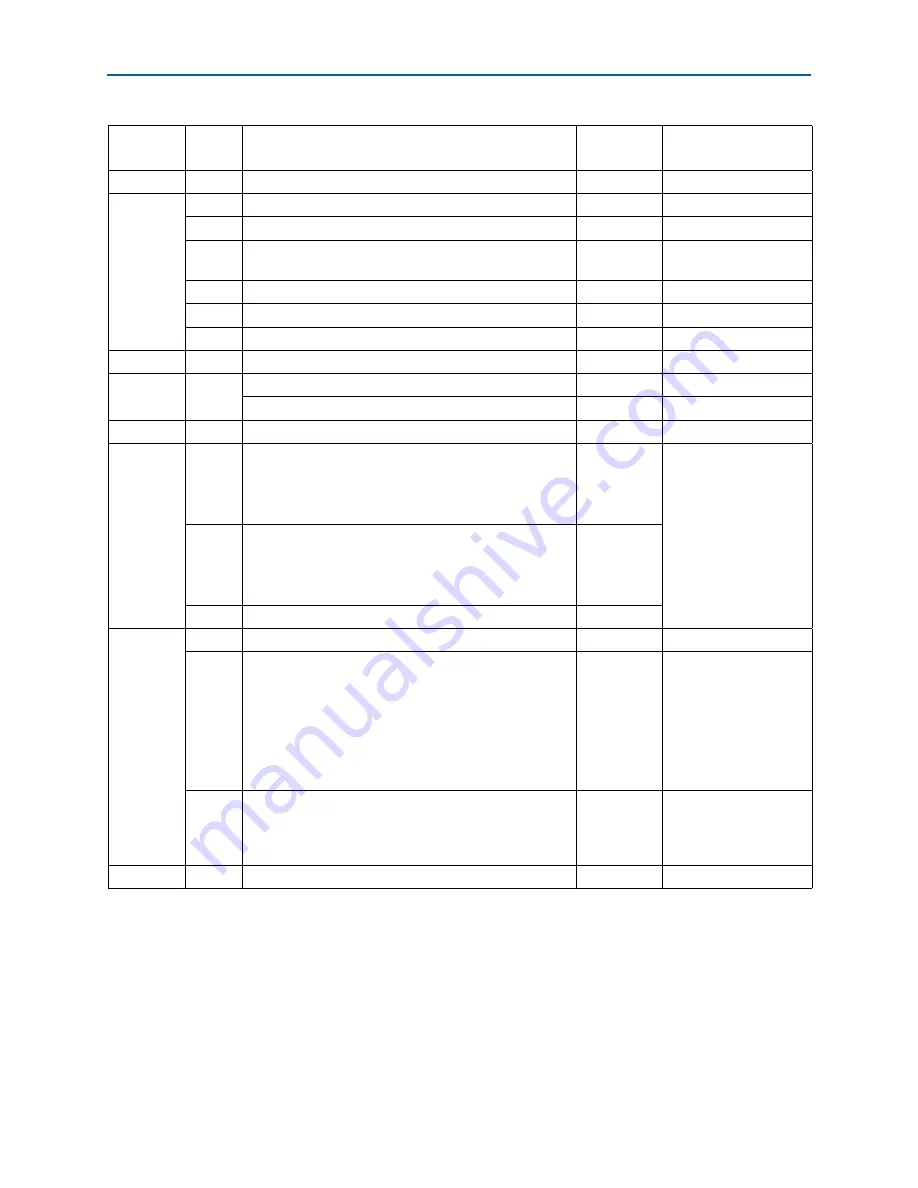

14–8

Chapter 14: Hard IP Reconfiguration and Transceiver Reconfiguration

Hard IP Reconfiguration Interface

Stratix V Hard IP for PCI Express

June 2012

Altera Corporation

0xAA

15:0

BAR4[159:144].

b’0

0xAB

BAR5[191:160].

b’0

0

BAR5[160]: I/O Space.

b’0

2:1

BAR5[162:161]: Memory Space (see bit settings for

BAR0).

b’0

3

BAR5[163]: Prefetchable.

b’0

BAR5[191:164]: Bar size mask.

b’0

15:4

BAR5[175:164].

b’0

0xAC

15:0

BAR5[191:176].

b’0

0xAD

15:0

Expansion BAR[223:192]: Bar size mask.

b’0

Expansion BAR[207:192].

b’0

0xAE

15:0

Expansion BAR[223:208].

b’0

0xAF

1:0

IO.

b’0

00: no IO windows.

01: IO 16 bit.

11: IO 32-bit.

3:2

Prefetchable.

b’0

00: not implemented.

01: prefetchable 32.

11: prefetchable 64.

15:4

Reserved.

—

B0

5:0

Reserved

—

—

6

Selectable de-emphasis, operates as specified in the

when operating at the 5.0GT/s

rate:

1: 3.5 dB

0: -6 dB.

This setting has no effect when operating at the 2.5GT/s

rate.

9:7

Transmit Margin. Directly drives the transceiver

tx_pipemargin

bits. Refer to the

Characteristics for Stratix V Devices

to determine what

V

OD

settings are available.

0xB1-FF

Reserved.

Table 14–1. Dynamically Reconfigurable Registers in the Hard IP Implementation (Part 8 of 8)

Address

Bits

Description

Default

Value

Additional Information