Chapter 15: Debugging

15–7

Link Hangs in L0 Due To Deassertion of tx_st_ready

June 2012

Altera Corporation

Stratix V Hard IP for PCI Express

rate[1:0]

[93:92]

[253:252]

The 2-bit encodings have the following meanings:

■

2’b01: Gen1 rate (2.5 Gbps)

■

2’b10: Gen2 rate (5.0 Gbps)

■

2’b13: Gen3 rate (8.0 Gbps)

■

2’b00: reserved

rxstatus0[2:0]

[91:89]

[251:249]

Receive status

<n>

. This signal encodes receive status

and error codes for the receive data stream and receiver

detection. The following encodings are defined:

■

3’b000: Received data OK.

■

3’b001: 1 SKP added.

■

3’b010: 1 SKP removed.

■

3’b011: Received detected.

■

3’b100: Both 8B/10B decode error and Receive

Disparity error.

■

3’b101: Elastic Buffer overflow.

■

3’b110: Elastic Buffer underflow.

■

3’b111: Reserved.

rxelecidle0

[88]

[248]

Indicates receiver detection of an electrical idle.

phystatus0

[87]

[247]

This signal communicates completion of several PHY

requests.

rxvalid0

[86]

[246]

Indicates symbol lock and valid data on rxdata0[31:0] and

rxdatak0[3:0]

rxblkst0

[85]

[245]

For Gen3 operation, indicates the start of a block.

rxsynchd0[1:0]

[84:83]

[244:243]

For Gen3 operation, specifies the block type. The

following encodings are defined:

■

2'b01: Ordered Set Block

■

2'b10: Data Block

rxdataskip0

[82]

[242]

For Gen3 operation. Allows the PCS to instruct the RX

interface to ignore the RX data interface for one clock

cycle. The following encodings are defined:

■

1’b0: RX data is invalid

■

1’b1: RX data is valid

rxdatak0[3:0]

[81:78]

[241:238]

These signals show the data and control received by Hard

P block from the other device.

rxdata0[31:0]

[77:46]

[237:206]

powerdown0[1:0]

[45:44]

[205:204]

The 4 encodings of these signals have the following

meanings:

■

2’b00: Phy is transmitting data.

■

2’b01: PHY is in electrical idle.

■

2’b10: PHY is in loopback mode.

■

2’b11: Illegal. Not defined.

rxpolarity0

[43]

[203]

When asserted, the PHY must invert the received data.

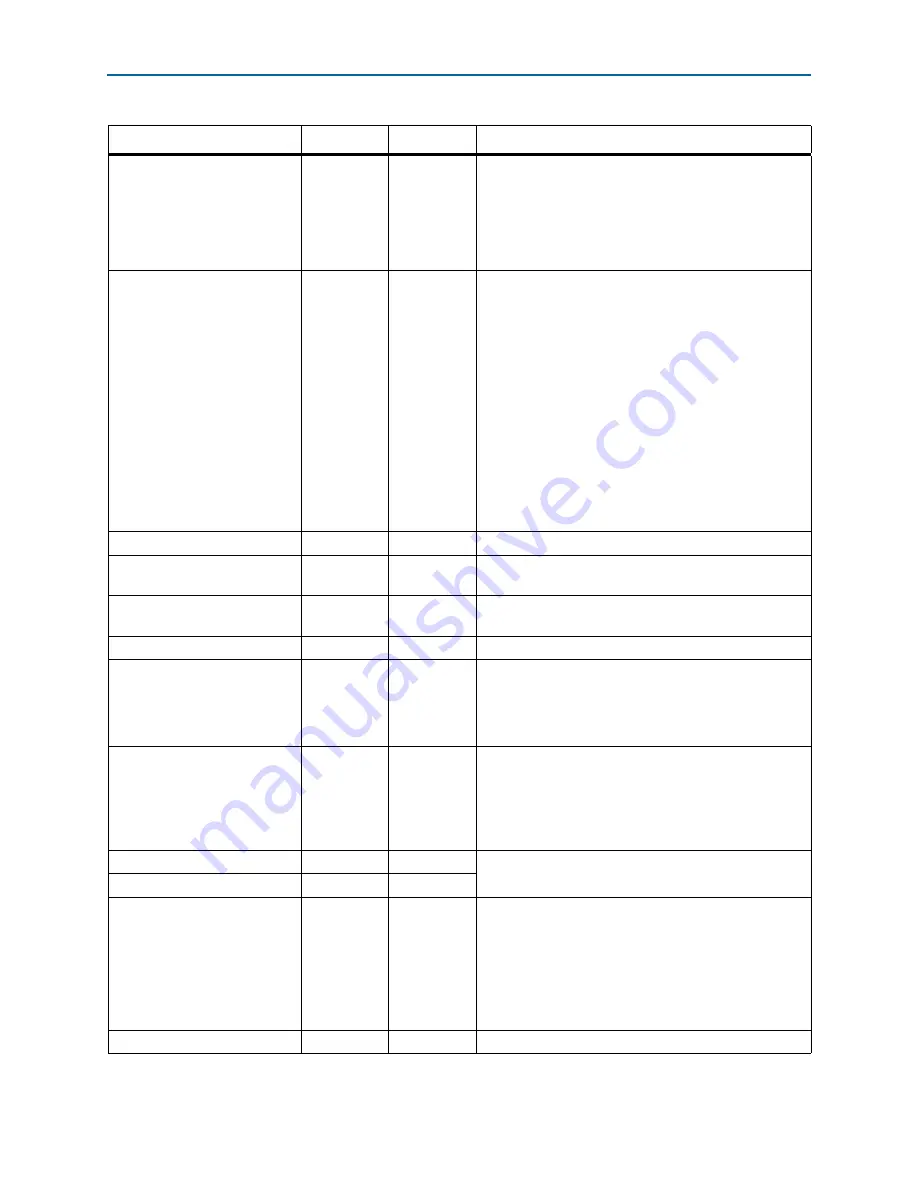

Table 15–3. PIPE Interface Signals (Part 2 of 3)

Signal Name

Lane 0

Lane 1

Description