Chapter 2: Getting Started with the Stratix V Hard IP for PCI Express

2–11

Qsys Design Flow

June 2012

Altera Corporation

Stratix V Hard IP for PCI Express

Qsys filters the component library and shows all components matching the text

string you entered.

4. Click on

Stratix V Hard IP for PCI Express

and then click the

+

Add

button. The

parameter editor appears.

The following sections provide step-by-step instructions to create the example design

in Qsys. If you prefer, you can copy the completed system from the Quartus II

software installation, and then go to

“Generating the Simulation Model Using Qsys”

. The file name for the completed Qsys system is:

<install_dir>

/ip/altera/altera_pcie/

altera_pcie_hip_ast_ed/example_design/sv/pcie_de_gen1_x8_ast128.qsys

.

Specify the Parameters for the Stratix V Hard IP for PCI Express

This section guides you through the process of specifying parameters for the Stratix V

Hard IP for PCI Express to create a Gen1 ×8 Endpoint.

1. Specify the

System Settings listed

2. Specify the

BAR

settings listed in

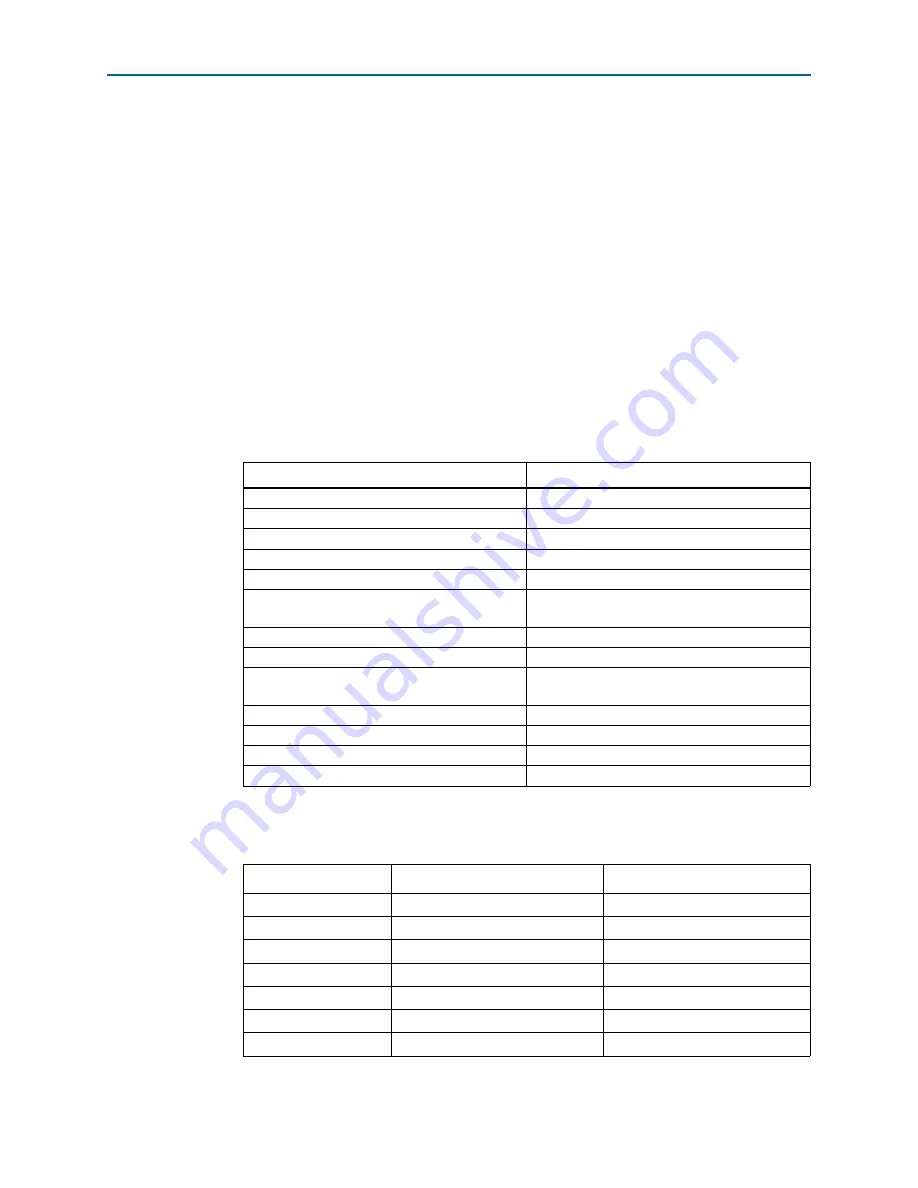

Table 2–8. System Settings Parameters

Parameter

Value

Number of Lanes

×8

Lane Rate

Gen 1 (2.5 Gbps)

Port type

Native Endpoint

PCI Express Base Specification version

2.1

Application interface

Avalon-ST 128 -bit

RX buffer credit allocation - performance for

received requests

Low

Reference clock frequency

100 MHz

Use 62.5 MHz application clock for ×1

Leave this option off

Use deprecated RX Avalon-ST data byte enable

port (rx_st_be)

Turn this option on

Enable byte parity ports on Avalon-ST interface

Leave this option off

Multiple packets per cycle

Leave this option off

Enable configuration via the PCIe link

Leave this option off

Enable Hard IP reconfiguration

Leave this option off

Table 2–9. Base Address Register and Expansion ROM Settings

BAR Number

TYPE

Size

0

64-bit Prefetchable Memory

256 MBytes - 28 bits

1

Disable this BAR

N/A

2

32-bit Non-Prefetchable Memory

1 KByte - 10 bits

3

Disable this BAR

N/A

4

Disable this BAR

N/A

5

Disable this BAR

N/A

Expansion ROM

Disabled

—