Chapter 7: Register Descriptions

7–3

Configuration Space Register Content

June 2012

Altera Corporation

Stratix V Hard IP for PCI Express

describes the MSI Capability structure.

describes the MSI-X Capability structure.

0x018

Secondary Latency

Timer

Subordinate Bus

Number

Secondary Bus

Number

Primary Bus Number

0x01C

Secondary Status

I/O Limit

I/O Base

0x020

Memory Limit

Memory Base

0x024

Prefetchable Memory Limit

Prefetchable Memory Base

0x028

Prefetchable Base Upper 32 Bits

0x02C

Prefetchable Limit Upper 32 Bits

0x030

I/O Limit Upper 16 Bits

I/O Base Upper 16 Bits

0x034

Reserved

Capabilities

Pointer

0x038

Expansion ROM Base Address

0x03C

Bridge Control

Interrupt Pin

Interrupt Line

Note to

(1) Refer to

for a comprehensive list of correspondences between the Configuration Space registers and the

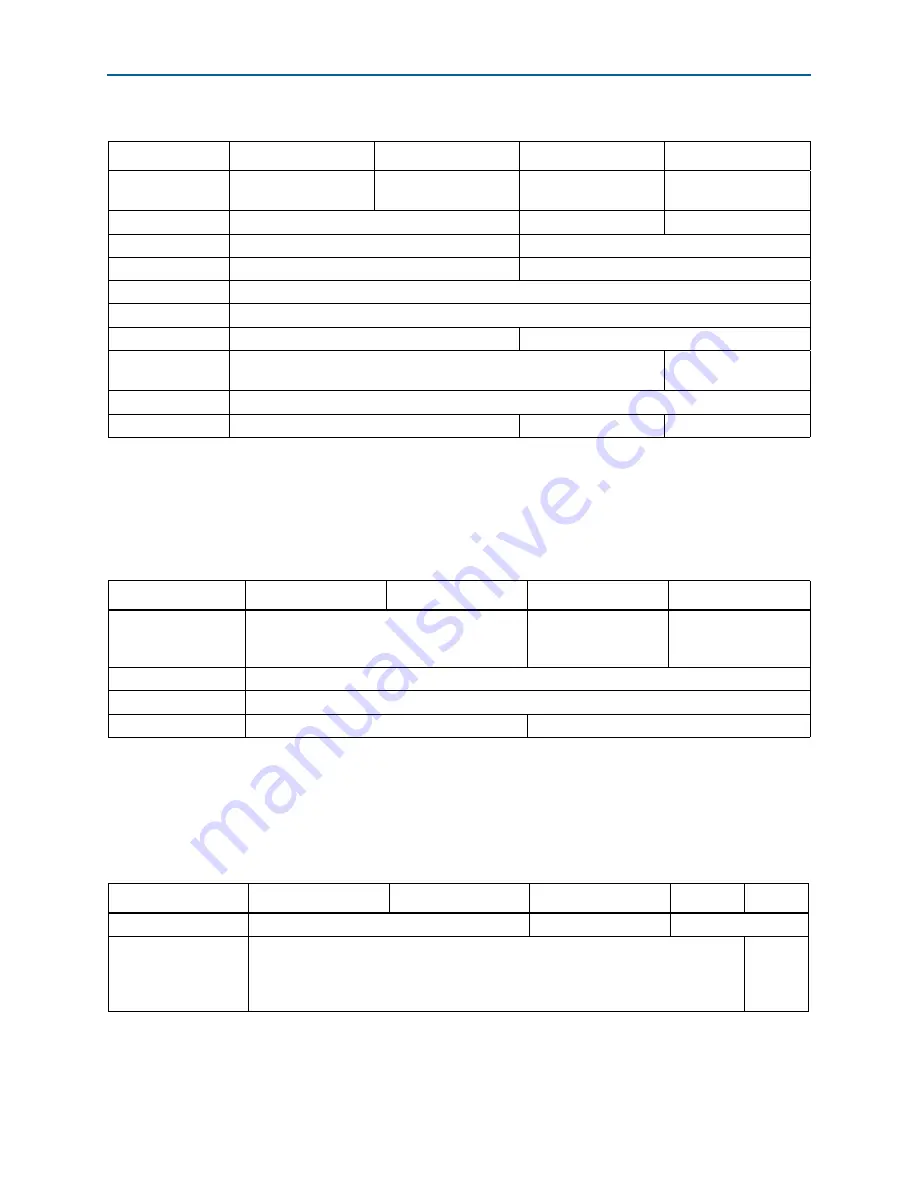

Table 7–3. PCI Type 1 Configuration Space Header (Root Ports) Rev3.0 Spec: Type 1 Configuration Space Header (Part 2

of 2)

Byte Offset

31:24

23:16

15:8

7:0

Table 7–4. MSI Capability Structure, Rev3.0 Spec: MSI Capability Structures

Byte Offset

31:24

23:16

15:8

7:0

0x050

Message Control

Configuration MSI Control Status Register Field

Next Cap Ptr

Capability ID

0x054

Message Address

0x058

Message Upper Address

0x05C

Reserved

Message Data

Notes to

:

(1) Specifies the byte offset within Stratix V Hard IP for PCI Express IP core’s address space.

(2) Refer to

for a comprehensive list of correspondences between the Configuration Space registers and the

Table 7–5. MSI-X Capability Structure, Rev3.0 Spec: MSI-X Capability Structures

Byte Offset

31:24

23:16

15:8

7:3

2:0

0x068

Message Control

Next Cap Ptr

Capability ID

0x06C