5–16

Chapter 5: IP Core Architecture

PCI Express Avalon-MM Bridge

Stratix V Hard IP for PCI Express

June 2012

Altera Corporation

The Avalon-MM RX master module port has an 8-byte datapath in 64-bit mode and a

16-byte datapath in 128-bit mode. The Qsys interconnect fabric handles mismatched

port widths transparently.

In the TX direction, the PCI Express to Avalon-MM Bridge uses the MSB of the PCI

Express address to identify one of the six BARs and then drives the unchanged LSB to

the Application Layer.

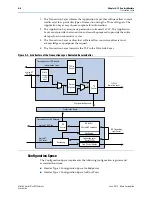

Avalon-MM-to-PCI Express Address Translation

The Avalon-MM address of a received request on the TX Avalon-MM slave port is

translated to the PCI Express address before the request packet is sent to the

Transaction Layer. You can specify up to 512 address pages and sizes ranging from

4 KByte to 4 GBytes when you customize your Avalon-MM Stratix V Hard IP for PCI

Express as described in

“Avalon to PCIe Address Translation Settings” on page 4–12

This address translation process proceeds by replacing the MSB of the Avalon-MM

address with the value from a specific translation table entry; the LSB remain

unchanged. The number of MSB to be replaced is calculated based on the total

address space of the upstream PCI Express devices that the Avalon-MM Hard IP for

PCI Express can access. The number of MSB bits is defined by the difference between

the maximum number of bits required to represent the address space supported by

the upstream PCI Express device minus the number of bits required to represent the

Size of address pages

which are the LSB pass-through bits (

N

). The

Size of address

pages

(

N

) is applied to all entries in the translation table.

Each of the 512 possible entries corresponds to the base address of a PCI Express

memory segment of a specific size. The segment size of each entry must be identical.

The total size of all the memory segments is used to determine the number of address

MSB to be replaced. In addition, each entry has a 2-bit field,

Sp[1:0]

, that specifies 32-

bit or 64-bit PCI Express addressing for the translated address. Refer to

. The most significant bits of the Avalon-MM address are used by the

interconnect fabric to select the slave port and are not available to the slave. The next

most significant bits of the Avalon-MM address index the address translation entry to

be used for the translation process of MSB replacement.

For example, if the core is configured with an address translation table with the

following attributes:

■

Number of Address Pages

—

16

■

Size of Address Pages

—

1 MByte

■

PCI Express Address Size

—

64 bits

then the values in

are:

■

N

= 20 (due to the 1 MByte page size)

■

Q

= 16 (number of pages)

■

M

= 24 (20 + 4 bit page selection)

■

P

= 64

In this case, the Avalon address is interpreted as follows:

■

Bits [31:24] select the TX slave module port from among other slaves connected to

the same master by the system interconnect fabric. The decode is based on the base

addresses assigned in Qsys.