•

General Options Parameters

on page 10-4

•

Additional Options Parameters

on page 10-7

•

PLL Reconfiguration Parameters

on page 10-10

•

Low Latency PHY Analog Parameters

on page 10-12

5. Click Finish to generate your parameterized Low Latency PHY IP Core.

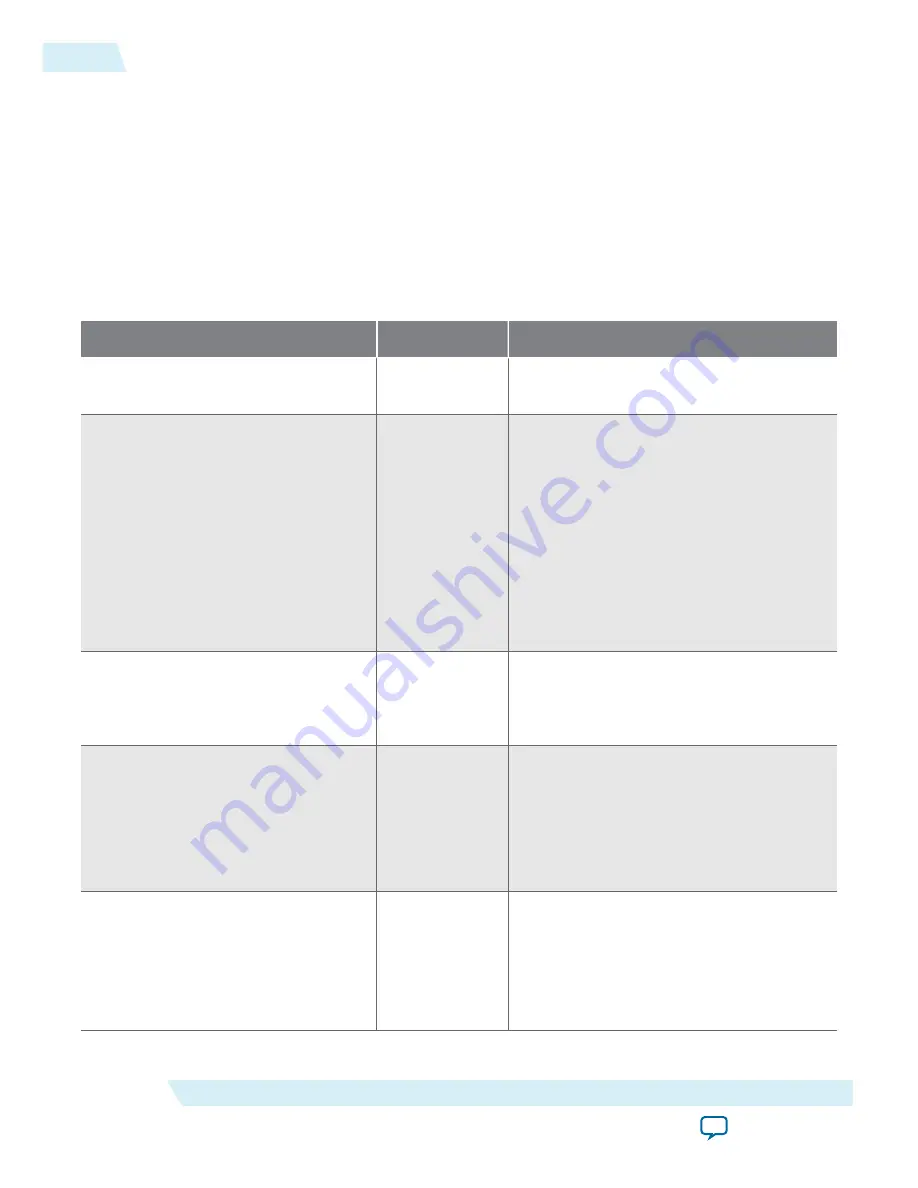

General Options Parameters

The following table lists the settings available on General Options tab:

Table 10-3: Low Latency PHY General Options

Name

Value

Description

Device family

Stratix V

This IP core is only available for Stratix V

devices.

Datapath type

Standard

10G

GT

The Low Latency PHY IP Core is part of a

Standard, 10G, or GT datapath. In most

cases the FPGA fabric transceiver interface

width determines the bandwidth of the

datapath; however, when the FPGA fabric

transceiver interface width is 32 or 40 bits,

you have the option of using either the

Standard datapath which is the default

mode, or changing to the 10G datapath by

selecting this option. Refer to

Table 10-4

Datapath Width Support

for a comprehen‐

sive list of datapath support.

Mode of operation

Duplex

RX

TX

Specifies the mode of operation as Duplex,

RX, or TX mode.

Number of lanes

1

-

32

Specifies the total number of lanes in each

direction. Stratix V devices include up to 32

GX channels (Standard or 10G) and up to 4

GT channels. You must instantiate each GT

channel in a separate Low Latency PHY IP

Core instance. You cannot specify both GX

and GT channels within the same instance.

Enable lane bonding

On/Off

When enabled, the PMA uses the same clock

source for up to 6 channels in a transceiver

bank, reducing clock skew.

Turn this option Off if you are using

multiple TX PLLs in a single Low Latency

PHY IP Core instance.

10-4

General Options Parameters

UG-01080

2015.01.19

Altera Corporation

Low Latency PHY IP Core

Send Feedback