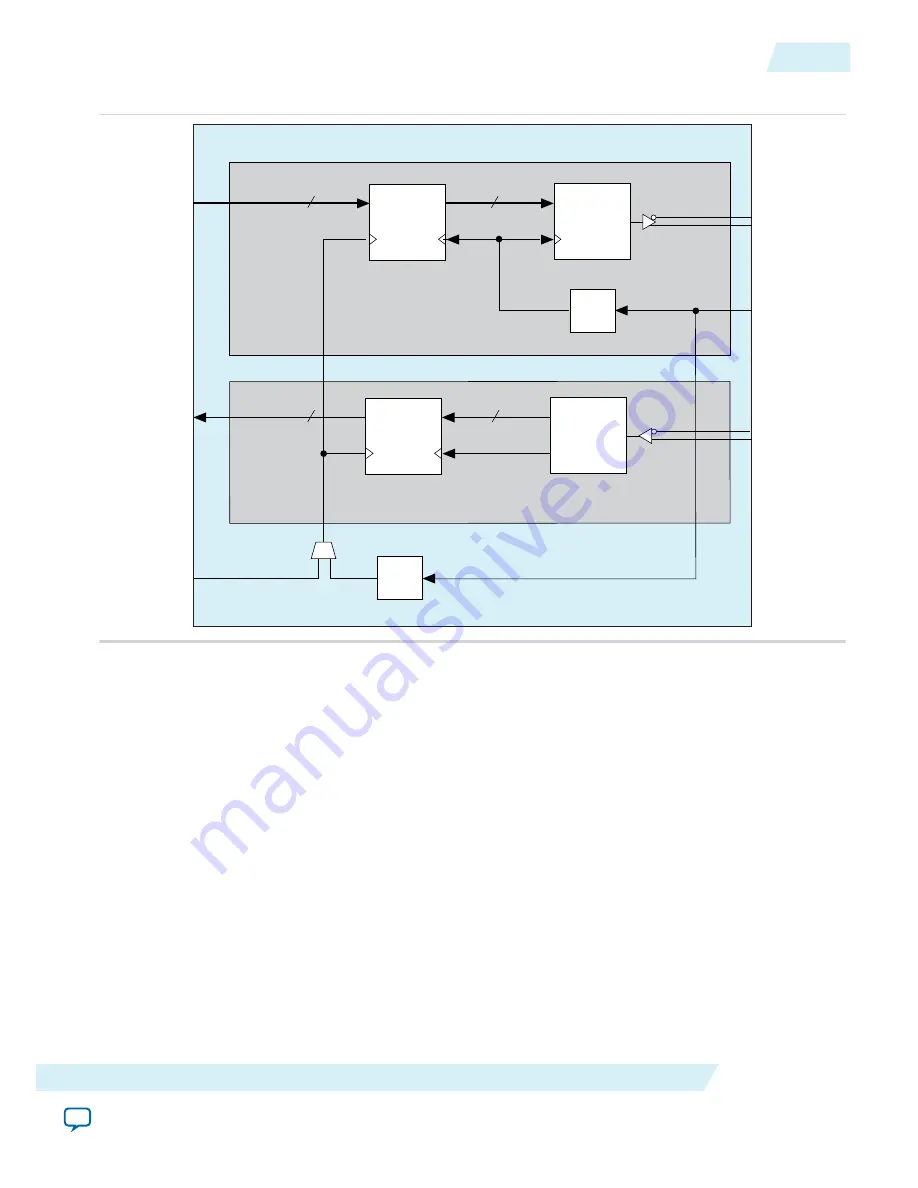

Figure 3-10: Stratix V Clock Generation and Distribution

pll_ref_clk

644.53125 MHz

10.3125

Gbps serial

257.8125

MHz

257.8125

MHz

156.25 MHz

10GBASE-R Hard IP Transceiver Channel - Stratix V

TX

RX

TX PCS

40

TX PMA

10.3125

Gbps serial

RX PCS

40

RX PMA

TX PLL

8/33

fPLL

xgmii_rx_clk

rx_coreclkin

xgmii_tx_clk

64-bit data, 8-bit control

64-bit data, 8-bit control

To ensure proper functioning of the PCS, the maximum PPM difference between the

pll_ref_clk

and

xgmii_tx_clk

clock inputs is 0 PPM. The FIFO in the RX PCS can compensate ±100 PPM between the

RX PMA clock and

xgmii_rx_clk

. You should use

xgmii_rx_clk

to drive

xgmii_tx_clk

. The CDR logic

recovers 257.8125 MHz clock from the incoming data.

10GBASE-R PHY Register Interface and Register Descriptions

The Avalon-MM PHY management interface provides access to the 10GBASER-R PHY PCS and PMA

registers. You can use an embedded controller acting as an Avalon-MM master to send read and write

commands to this Avalon-MM slave interface.

UG-01080

2015.01.19

10GBASE-R PHY Register Interface and Register Descriptions

3-23

10GBASE-R PHY IP Core

Altera Corporation

Send Feedback