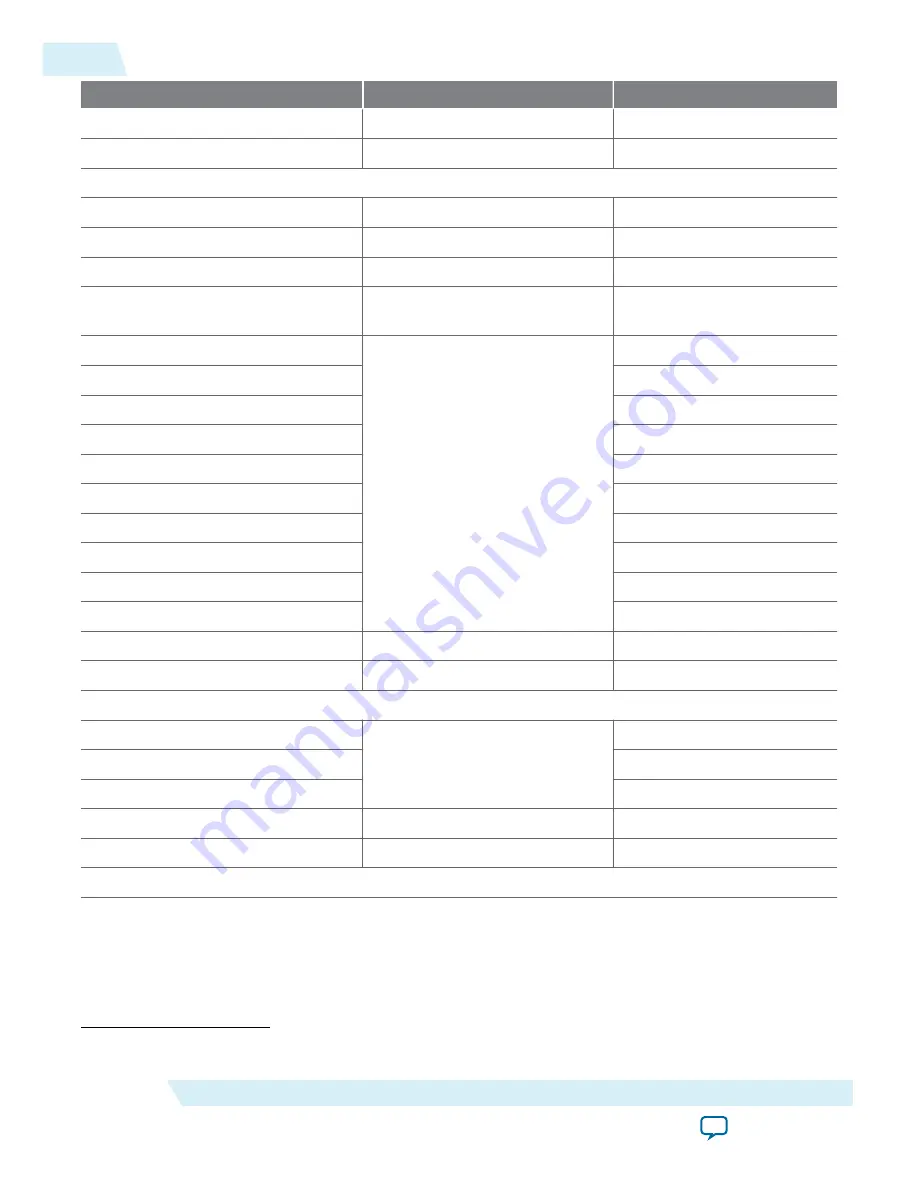

Stratix IV GX Device Signal Name

(21)

Stratix V GX Device Signal Name

Width

pipephydonestatus

pipe_phystatus

[<

n

>-1:0]

pipestatus

pipe_rxstatus

[3<

n

>-1:0]

Non-PIPE Ports

rx_pll_locked

rx_is_lockedtoref

[<

n

>--1:0]

rx_freqlocked

rx_is_lockedtodata

[<

n

>--1:0]

pll_locked

pll_locked

1

rx_syncstatus

rx_syncstatus

(also management

interface)

[(<

d

>/8)*<

n

>-1:0]

rx_locktodata

These signals are now available as

control and status registers. Refer to

the “Register Interface and Register

Descriptions”.

[<

n

>-1:0]

rx_locktorefclk

[<

n

>-1:0]

tx_invpolarity

[<

n

>-1:0]

rx_errdetect

[(<

d

>/8)*<

n

>-1:0]

rx_disperr

[(<

d

>/8)*<

n

>-1:0]

rx_patterndetect

[(<

d

>/8)*<

n

>-1:0]

tx_phase_comp_fifo_error

[<

n

>-1:0]

rx_phase_comp_fifo_error

[<

n

>-1:0]

rx_signaldetect

[<

n

>-1:0]

rx_rlv

[<

n

>-1:0]

rx_datain

rx_serial_data

[<

n

>-1:0]

tx_dataout

tx_serial_data

[<

n

>-1:0]

Reconfiguration

cal_blk_clk

These signals are included in the

reconfig_to_xcvr bus

1

reconfig_clk

1

fixedclk

1

reconfig_togxb

reconfig_to_xcvr

Variable

reconfig_fromgxb

reconfig_from_xcvr

Variable

Avalon MM Management Interface

(21)

<

n

> = the number of lanes. <

d

> = the total deserialization factor from the pin to the FPGA fabric.

20-10

Differences Between PHY IP Core for PCIe PHY (PIPE) Ports for Stratix IV and Stratix V

Devices

UG-01080

2013.12.20

Altera Corporation

Migrating from Stratix IV to Stratix V Devices Overview

Send Feedback