ALTGX

(23)

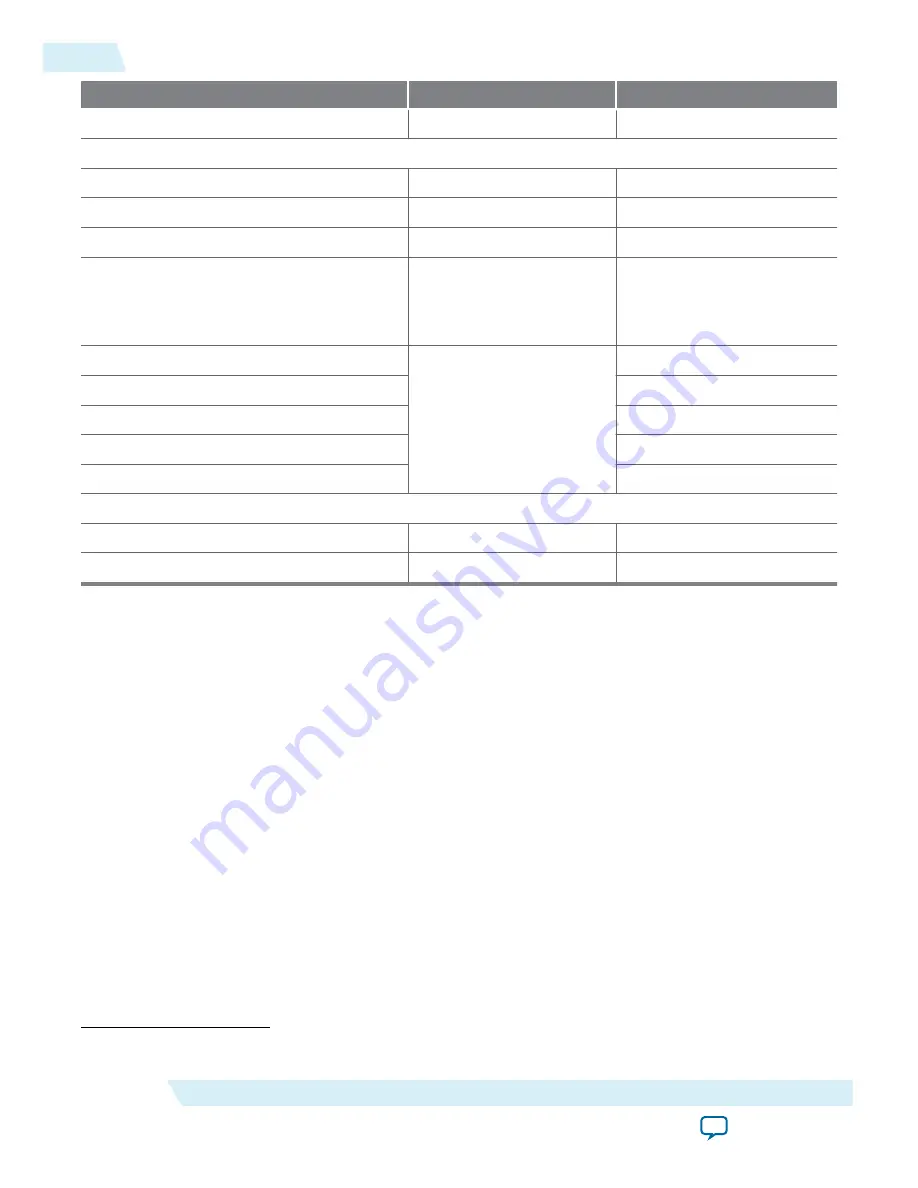

Custom PHY

Width

rx_freqlocked

rx_is_lockedtodata

[<

n

>-1:0]

Transceiver Control and Status Signals

gxb_powerdown

phy_mgmt_clk_reset

—

rx_dataoutfull

—

—

tx_dataoutfull

—

—

rx_pll_locked

There are both

pll_locked

and rx_pll_clocked in Stratix

IV. Stratix V only has

pll_

locked

.

—

rx_clkout

These signals are now

available as control and status

registers. Refer to Register

Descriptions.

—

rx_phase_comp_fifo_error

—

rx_seriallpbken

—

tx_phase_comp_fifo_error

—

tx_invpolarity

—

Transceiver Reconfiguration

reconfig_togxb[3:0]

reconfig_to_xcvr

Variable

reconfig_fromgxb[16:0]

reconfig_from_xcvr

Variable

Related Information

Register Interface and Register Descriptions

on page 9-27

(23)

<

n

> = the number of lanes. <

d

> = the total deserialization factor from the pin to the FPGA fabric.

20-14

Differences Between Custom PHY Ports in Stratix IV and Stratix V Devices

UG-01080

2013.12.20

Altera Corporation

Migrating from Stratix IV to Stratix V Devices Overview

Send Feedback