Status Registers Model from IEEE 488.2

M370185-01

5-27

5

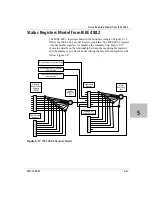

Status Registers Model from IEEE 488.2

The IEEE 488.2 registers shown in the bottom rectangle of Figure 5-16

follow the IEEE 488.2 model for status registers. The IEEE 488.2 register

only has enable registers for masking the summary bits. Figure 5-17

shows the details on the relationship between the mask/enable registers

and the summary bits. Sections describing the bits for both registers will

follow Figure 5-17.

Figure 5-17

IEEE 488.2 Register Model

SERS Enable

Register

0

1

2

3

4

5

6

7

Standard

Event Status

Register

(SESR )

+

SESR

Summary

Bit

...

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

&

&

&

&

&

&

&

&

Status Byte

Enable Register

0

1

2

3

4

5

6

7

Status Byte

Register

&

&

&

&

&

&

&

+

MSS

Summary

Bit

QUEStionable SCPI Register

Summary Bit

OPERational SCPI Register

Summary Bit

Error/Event Queue Status Flag

Summary of Contents for Soresen XTR 100-8.5

Page 2: ......

Page 16: ...xiv ...

Page 28: ...1 8 ...

Page 50: ...Local Operation 3 8 M370185 01 Figure 3 3 Front Panel Menu System ...

Page 93: ...Using Multiple Power Supplies M370185 01 3 51 3 ...

Page 94: ...Local Operation 3 52 M370185 01 ...

Page 128: ...Analog Programming APG and Isolated Analog Programming ISOL 4 34 M370185 01 ...

Page 198: ...Remote Operation 5 70 M370185 01 ...

Page 261: ...SCPI Command Tree M370185 01 A 35 A ...

Page 262: ...A 36 ...

Page 279: ...Index M370185 01 IX 3 described 3 7 3 36 number available 3 36 stored values 3 36 ...

Page 280: ...IX 4 ...