Detailed Description

Analog Section

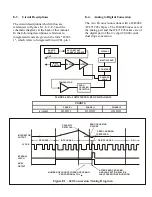

Figures E2 diagrams A thru D shows the

equivalent circuit of the analog section in 3

different phases of operation. The system will

perform conversions at a rate determined by the

clock frequency 40,002 clock periods per cycle.

(see Figure E1B shown earlier in this chapter for

details of conversion timing).

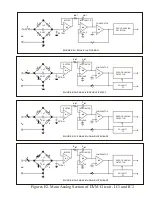

Auto-Zero Phase I (Figure E2A)

During the Auto-Zero, the input of the buffer is

connected to V REF through switch 2, and switch

3 closes a loop around the integrator and

comparator, the purpose of which is to charge the

Auto-Zero capacitor until the integrator output

does not change with time. Also, switches 1 and 2

recharge the reference capacitor to V REF.

Input Integrate Phase II (Figure E2B)

During Input Integrate the Auto-Zero loop is

opened and the Analog Input is connected to the

Buffer Input through switch 4 and C REF if the

input signal is zero, the buffer, integrator and

comparator will see the same voltage that existed

in the previous state (Auto-Zero). Thus, the

integrator output will not change but will remain

stationary during the entire input integrate cycle.

If V

IN

is not equal to zero, and an unbalanced

condition exists compared to the Auto-Zero

Phase, the integrator will generate a ramp whose

slope is proportional to V

IN

.

Deintegrate Phase II (Figures E2C and Figures

E2D)

During the Deintegrate phase, switch 5 is closed

and a voltage which is V REF more positive than

during Auto-Zero is impressed on the BUFFER

INPUT. Thus, the reference capacitor stores the

equivalent voltage. This returns the output of the

integrator to the zero-crossing point established in

Phase I. The time, or number of counts, required

to do this is proportional to the input voltage.

E-4-1. Reference Voltage

The precision reference voltage required to do

the A/D conversion is developed by IC201. The

zener voltage is attenuated to approximately -

0.5V. This voltage is applied to IC2-7.

E-4-2. LED Display

The output format from IC2 is in Binary Coded

Decimal (BCD) format. Each digit is scanned

for 10 clock pulses. The scan sequence is D5 D4

D3 D2 D1. This drives Q1 thru Q5, which in

turn drivers the seven segment displays. The

BCD data is converted to seven segment format

by IC4. When the 620A-4 electronics are in

open circuit or over-range mode the display

flashes “

0000"

. IC5 is a 1 MHz oscillator

which is divided by 10 by IC6. The 100 KHz

clock output then goes to IC2.

E-5.

Ohms-To-DC Converter

The ohms-to-DC converter generates a constant

current which is passed through the device under

test to develop the voltage measured by the A/D

converter.

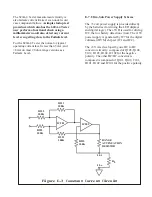

E-5-1. Constant Current Source

The constant current source is composed of

IC201, IC202, Q202, D203 and their associated

components. The input to the constant current

source is approxi1.05 volts, developed

at IC201-7 and connected to IC201-13 through

R209 and R210. The heart of the constant

current source is the voltage-to-current

converter. A simplified schematic of this circuit

is shown in Figure E-4 and described in Section

E-5-2. The amplifier of IC201-12 is an inverter,

and its output is applied to IC201-9. The

amplifier of IC201-8 has unity gain due to the

feedback through R213. Its output is applied

to the inverting input of IC202-3. The output of

IC202-6 provides feedback to the non-inverting

input of IC201-10. This circuit operates to

maintain the inverting input at IC202-3 and the

non-inverting input at IC202-2 at the same

potential.